PCI Express是新一代的汇流排接口。早在2001年的春季,英特尔公司就提出了要用新一代的技术取代PCI汇流排和多种晶片的内部连线,并称之为第三代I/O汇流排技术。随后在2001年底,包括Intel、AMD、DELL、IBM在内的20多家业界主导公司开始起草新技术的规范,并在2002年完成,对其正式命名为PCI Express。它採用了目前业内流行的点对点串列连线,比起PCI以及更早期的计算机汇流排的共享并行架构,每个设备都有自己的专用连线,不需要向整个汇流排请求频宽,而且可以把数据传输率提高到一个很高的频率,达到PCI所不能提供的高频宽。

基本介绍

- 中文名:汇流排接口

- 外文名:PCI Express

- 时间:2001年的春季

- 公司:英特尔公司

基本概念

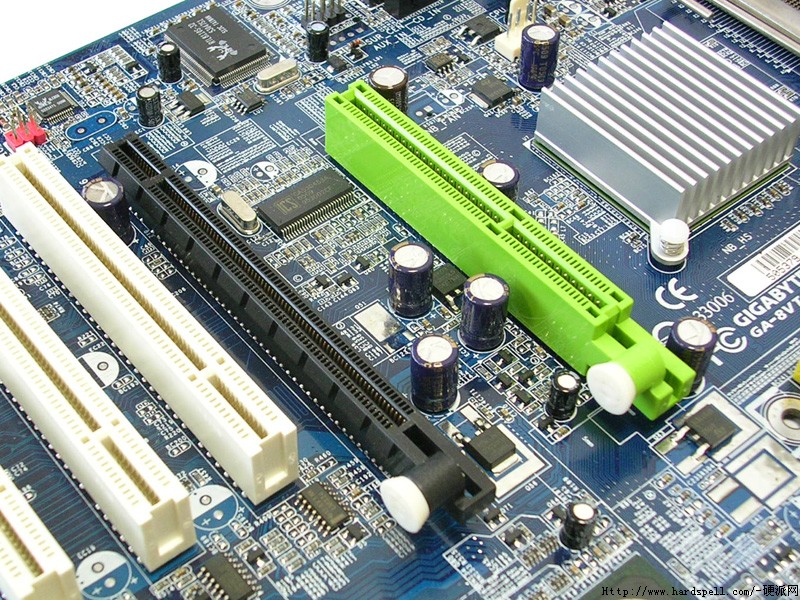

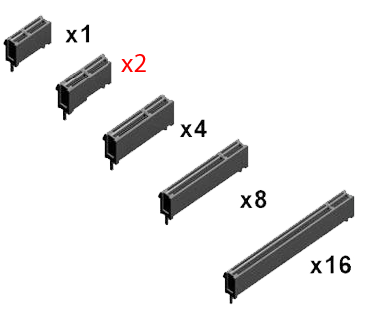

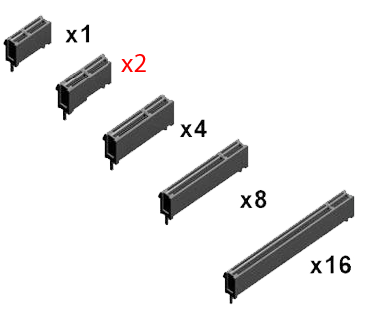

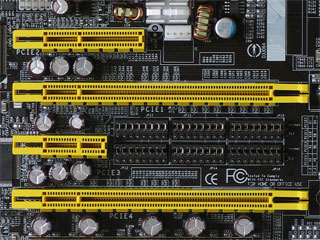

PCI Express的接口根据汇流排位宽不同而有所差异,包括X1、X4、X8以及X16(X2模式将用于内部接口而非插槽模式)。较短的PCI Express卡可以插入较长的PCI Express插槽中使用。PCI Express接口能够支持热拔插,这也是个不小的飞跃。PCI Express卡支持的三种电压分别为+3.3V、3.3Vaux以及+12V。用于取代AGP接口的PCI Express接口位宽为X16,将能够提供5GB/s的频宽,即便有编码上的损耗但仍能够提供4GB/s左右的实际频宽,远远超过AGP 8X的2.1GB/s的频宽。

PCI Express规格从1条通道连线到32条通道连线,有非常强的伸缩性,以满足不同系统设备对数据传输频宽不同的需求。例如,PCI Express X1规格支持双向数据传输,每向数据传输频宽250MB/s,PCI Express X1已经可以满足主流声效晶片、网卡晶片和存储设备对数据传输频宽的需求,但是远远无法满足图形晶片对数据传输频宽的需求。因此,必须採用PCI Express X16,即16条点对点数据传输通道连线来取代传统的AGP汇流排。PCI Express X16也支持双向数据传输,每向数据传输频宽高达4GB/s,双向数据传输频宽有8GB/s之多,相比之下,广泛採用的AGP 8X数据传输只提供2.1GB/s的数据传输频宽。

儘管PCI Express技术规格允许实现X1(250MB/秒),X2,X4,X8,X12,X16和X32通道规格,但是依形式来看,PCI Express X1和PCI Express X16将成为PCI Express主流规格,同时晶片组厂商将在南桥晶片当中添加对PCI Express X1的支持,在北桥晶片当中添加对PCI Express X16的支持。除去提供极高数据传输频宽之外,PCI Express因为採用串列数据包方式传递数据,所以PCI Express接口每个针脚可以获得比传统I/O标準更多的频宽,这样就可以降低PCI Express设备生产成本和体积。另外,PCI Express也支持高阶电源管理,支持热插拔,支持数据同步传输,为优先传输数据进行频宽最佳化。

在兼容性方面,PCI Express在软体层面上兼容的PCI技术和设备,支持PCI设备和记忆体模组的初始化,也就是说驱动程式、作业系统无需推倒重来,就可以支持PCI Express设备。PCI Express是新一代能够提供大量频宽和丰富功能以实现令人激动的新式图形套用的全新架构。PCI Express可以为频宽渴求型套用分配相应的频宽,大幅提高中央处理器(CPU)和图形处理器(GPU)之间的频宽。对最终用户而言,他们可以感受影院级图象效果,并获得无缝多媒体体验。

PCI Express的主要优势就是数据传输速率高,目前最高的16X 2.0版本可达到10GB/s,而且还有相当大的发展潜力。PCI Express也有多种规格,从PCI Express 1X到PCI Express 16X,能满足一定时间内出现的低速设备和高速设备的需求。PCI-Express最新的接口是PCIe 3.0接口,其比特率为8GT/s,约为上一代产品频宽的两倍,并且包含发射器和接收器均衡、PLL改善以及时钟数据恢复等一系列重要的新功能,用以改善数据传输和数据保护性能。像INTEL、IBM、、LSI、OCZ、、三星(计画中)、SanDisk、STEC、SuperTalent和东芝(计画中)等,而针对海量的数据增长使得用户对规模更大、可扩展性更强的系统所套用,PCIe 3.0技术的加入最新的LSI MegaRAID控制器及HBA产品的出色性能,就可以实现更大的系统设计灵活性。

PCI Express採用串列方式传输Data。它和原有的ISA、PCI和AGP汇流排不同。这种传输方式,不必因为某个硬体的频率而影响到整个系统性能的发挥。当然了,整个系统依然是一个整体,但是我们可以方便的提高某一频率低的硬体的频率,以便系统在没有瓶颈的环境下使用。以串列方式提升频率增进效能,关键的限制在于採用什幺样的物理传输介质。人们普遍採用铜线路,而理论上铜这个材质可以提供的传输极限是10 Gbps。这也就是为什幺PCI Express的极限传输速度的答案。

因为PCI Express工作模式是一种称之为“电压差式传输”的方式。两条铜线,通过相互间的电压差来表示逻辑符号0和1。以这种方式进行资料传输,可以支持极高的运行频率。所以在速度达到10Gbps后,只需换用光纤(Fibre Channel)就可以使之效能倍增。

PCI Express是下一阶段的主要传输汇流排频宽技术。然而,GPU对汇流排频宽的需求是子系统中最高的,显而易见的是,视频在PCI Express应占有一定的分量。显然,PCI Express的提出,并非是汇流排形式的一个结束。恰恰相反,其技术的成熟仍旧需要这个时间。当然了,趁这个时间,那些晶片、主机板、视频等厂家是否能出来支持是PCI Express发展的关键。

PCI-Express是最新的汇流排和接口标準,它原来的名称为“3GIO”,是由英特尔提出的,很明显英特尔的意思是它代表着下一代I/O接口标準。交由PCI-SIG(PCI特殊兴趣组织)认证发布后才改名为“PCI-Express”。这个新标準将全面取代现行的PCI和AGP,最终实现汇流排标準的统一。它的主要优势就是数据传输速率高,目前最高可达到10GB/s以上,而且还有相当大的发展潜力。PCI Express也有多种规格,从PCI Express 1X到PCI Express 16X,晶片组。当然要实现全面取代PCI和AGP也需要一个相当长的过程,就象当初PCI取代ISA一样,都会有个过渡的过程。

起源和现状

2001年春季的IDF上Intel正式公布PCI Express,是取代PCI汇流排的第三代I/O技术,也称为3GIO。该汇流排的规范由Intel支持的AWG(Arapahoe Working Group)负责制定。2002 年4月17日,AWG正式宣布3GIO 1.0规范草稿制定完毕,并移交PCI-SIG进行审核。开始的时候大家都以为它会被命名为Serial PCI(受到串列ATA的影响),但最后却被正式命名为PCI Express。2006年正式推出Spec2.0(2.0规范)。 WY576-F2 Intel82576

WY576-F2 Intel82576

WY576-F2 Intel82576

WY576-F2 Intel82576PCI Express汇流排技术的演进过程,实际上是计算系统I/O接口速率演进的过程。PCI汇流排是一种33MHz@32bit或者66MHz@64bit的并行汇流排,汇流排频宽为133MB/s到最大533MB/s,连线在PCI汇流排上的所有设备共享133MB/s~533MB/s频宽。这种汇流排用来应付音效卡、10/100M网卡以及USB 1.1等接口基本不成问题。随着计算机和通信技术的进一步发展,新一代的I/O接口大量涌现,比如千兆(GE)、万兆(10GE)的乙太网技术、4G/8G的FC技术,使得PCI汇流排的频宽已经无力应付计算系统内部大量高频宽并行读写的要求,PCI汇流排也成为系统性能提升的瓶颈,于是就出现了PCI Express汇流排。PCI Express汇流排技术在当今新一代的存储系统已经普遍的套用。PCI Express汇流排能够提供极高的频宽,来满足系统的需求。

PCI-E 3.0规范也已经确定,其编码数据速率,比同等情况下的PCI-E 2.0规范提高了一倍,X32连线埠的双向速率高达32Gbps。

诞生和概念

虽然,除了3D显示卡以外,直到现在还没有哪个计算机配件脱离PCI汇流排的束缚另起炉灶,诸如千兆网卡、音效卡、RAID卡等都还在循规蹈矩的奉行着PCI规范,但,PC技术的快速发展已经让PCI汇流排越来越显现出不足,尤其是最近的千兆网路以及视频套用等外设,会使PCI可怜的133MB/s频宽难以承受,当几个类似外设同时满负荷运转,PCI汇流排几近瘫痪。不但如此,随着技术的不断进步,PCI电压难以降低的缺陷越来越凸出出来,PCI规范已经成为PC系统的发展桎梏,彻底升级换代迫在眉睫。

到了2001年,在Intel春季的IDF上,Intel正式公布了旨在取代PCI汇流排的第三代I/O技术,该规范由Intel 支持的AWG(Arapahoe Working Group)负责制定,并称之为第三代I/O汇流排技术(3rd Generation I/O,也就是3GIO),也就是后来的PCI Express汇流排规范。不过在公布之初,套用环境、配套设备还不是很完善,并不为人们所关注。到了2002年4月17日,AWG正式宣布3GIO 1.0规范草稿制定完毕,并移交PCI-SIG进行审核,该规范最终却被命名为PCI Express,而到了2003年Intel春季IDF上,Intel正式公布了PCI Express的产品开发计画,PCI Express最终走向套用。

PCI-E 3.0

常见的显示卡都是PCI-E 2.0标準的,制定于2007年,速率5GT/s,x16通道频宽可达8GB/s。按照原先的路线图,PCI-E 3.0标準将在2010年进入市场,不过实际上却是2010年才完成PCI-E 3.0标準的最终方案,而直到一年后HD 7970发布才真正有显示卡支持PCI-E 3.0。

PCI-E 3.0:频宽更高、延迟更低

与PCI-E 2.0相比,PCI-E 3.0的目标是频宽继续翻倍达到10GB/s,要实现这个目标就要提高速度,PCI-E 3.0的信号频率从2.0的5GT/s提高到8GT/s,编码方案也从原来的8b/10b变为更高效的128b/130b,其他规格基本不变,每周期依然传输2位数据,支持多通道并行传输。

除了频宽翻倍带来的数据吞吐量大幅提高之外,PCI-E 3.0的信号速度更快,相应地数据传输的延迟也会更低。此外,针对软体模型、功耗管理等方面也有具体最佳化。简而言之,PCI-E 3.0就跟高速路一样,车辆跑得更快,发车间隔更低,座位更舒适。

特点和长处

PCI Express汇流排是一种完全不同于过去PCI汇流排的一种全新汇流排规范,与PCI汇流排共享并行架构相比,PCI Express汇流排是一种点对点串列连线的设备连线方式,点对点意味着每一个PCI Express设备都拥有自己独立的数据连线,各个设备之间并发的数据传输互不影响,而对于过去PCI那种共享汇流排方式,PCI汇流排上只能有一个设备进行通信,一旦PCI汇流排上挂接的设备增多,每个设备的实际传输速率就会下降,性能得不到保证。PCI Express以点对点的方式处理通信,每个设备在要求传输数据的时候各自建立自己的传输通道,对于其他设备这个通道是封闭的,这样的操作保证了通道的专有性,避免其他设备的干扰。

在传输速率方面,PCI Express汇流排利用串列的连线特点将能轻鬆将数据传输速度提到一个很高的频率,达到远超出PCI汇流排的传输速率。PCI Express的接口根据汇流排位宽不同而有所差异,包括x1、x4、x8以及x16(x2模式将用于内部接口而非插槽模式),其中X1的传输速度为250MB/s,而X16就是等于16倍于X1的速度,即是4GB/s。与此同时,PCI Express汇流排支持双向传输模式,还可以运行全双工模式,它的双单工连线能提供更高的传输速率和质量,它们之间的差异跟半双工和全双工类似。因此连线的每个装置都可以使用最大频宽,PCI Express接口设备将有着比PCI设备优越的多的资源可用。

除了这些,PCI Express设备能够支持热拔插以及热交换特性,支持的三种电压分别为+3.3V、3.3Vaux以及+12V。考虑到显示卡功耗的日益上涨,PCI Express而后在规范中改善了直接从插槽中取电的功率限制,16x的最大提供功率达到了70W,比AGP 8X接口有了很大的提高。基本可以满足未来中高端显示卡的需求。这一点可以从AGP、PCI Express两个不同版本的6600GT上就能明显地看到,后者并不需要外接电源。

可以看到PCI Express只是南桥的扩展汇流排,它与作业系统无关,所以也保证了它与原有PCI的兼容性,也就是说在很长一段时间内在主机板上PCI Express接口将和PCI接口共存,这也给用户的升级带来了方便。由此可见,PCI Express最大的意义在于它的通用性,不仅可以让它用于南桥和其他设备的连线,也可以延伸到晶片组间的连线,甚至也可以用于连线图形晶片,这样,整个I/O系统将重新统一起来,将更进一步简化计算机系统,增加计算机的可移植性和模组化。PCI Express已经为PC的未来发展重新铺设好了路基,下面就要看PCI Express产品的套用情况了。

规格比较

PCI Express x16 插槽 WY5715F BCM5715S

WY5715F BCM5715S

WY5715F BCM5715S

WY5715F BCM5715SPCI Express x1 插槽

PCIe的规范主要是为了提升电脑内部所有汇流排的速度,因此频宽有多种不同规格标準,其中PCIe x16是专为显示卡所设计的部分。AGP的资料传输效率最高为2.1GB/s,不过对上PCIe x16的8GB/s,很明显的就分出胜负,但8GB/s只有指资料传输的理想值,并不是使用PCIe接口的显示卡,就能够有突飞猛进的效能表现,实际的测试数据上并不会有这幺大的差异存在。

传输通道数 | 脚Pin总数 | 主接口区Pin数 | 总 长 度 | 主接口区 长度 |

x1 | 36 | 14 | 25 mm | 7.65 mm |

x4 | 64 | 42 | 39 mm | 21.65 mm |

x8 | 98 | 76 | 56 mm | 38.65 mm |

x16 | 164 | 142 | 89 mm | 71.65 mm |

规格 | 汇流排宽度 | 工作时脉 | 传输速率 |

PCI 2.3 | 32 位元 | 33/66 MHz | 133/266 MiB/s |

PCI-X 1.0 | 64 位元 | 66/100/133 MHz | 533/800/1066 MiB/s |

PCI-X 2.0(DDR) | 64 位元 | 133 MHz | 2.1 GiB/s |

PCI-X 2.0(QDR) | 64 位元 | 133 MHz | 4.2 GiB/s |

AGP 2X | 32 位元 | 66 MHz | 532 MiB/s |

AGP 4X | 32 位元 | 66 MHz | 1.0 GiB/s |

AGP 8X | 32 位元 | 66 MHz | 2.1 GiB/s |

PCI-E 1X | 8 位元 | 2.5 GHz | 512 MiB/s(双工) |

PCI-E 2X | 8 位元 | 2.5 GHz | 1.0 GiB/s(双工) |

PCI-E 4X | 8 位元 | 2.5 GHz | 2.0 GiB/s(双工) |

PCI-E 8X | 8 位元 | 2.5 GHz | 4.0 GiB/s(双工) |

PCI-E 16X | 8 位元 | 2.5 GHz | 8.0 GiB/s(双工) |

甚至对于某些 PCI-E 1X插槽,我们完全可以将其锯开(这样有可能会失去质保),比如可以用来插上NVIDIA的显示卡做为物理加速卡与ATI显示卡一同工作。

协定问题

在开发第一块基于PCI Express的SoC过程中,ClearSpeed公司为了在有限的时间和预算条件下确保PCI Express协定一致性而面临重重困难。PCI Express是一种複杂的协定,具有特别大的覆盖範围。从管理的角度看,保证协定一致性没有其它更好的方法,只有採用标準驱动的验证过程。遗憾的是,即使做了上千次覆盖相关场景的测试,仍留有相当大的覆盖漏洞,从而使得这个方法没有可预测性,成本也很高。而另外一种普通的随机测试方法也没有足够的可预测性。

ClearSpeed公司开始意识到,理想的方法可以产生显着的好处:它能最小化技术开发工作量,同时最大化测试套用控制。ClearSpeed公司率先採用Cadence公司提供的商用化PCIe验证IP。这种验证IP被称为UVC,包含了一致性管理系统(CMS),该系统将覆盖空间划分和映射到了PCIe规范。CMS还提供受限随机测试(称为测试序列)形式的一致性测试套件,用于自动取得针对每个PCIe规范部分的高功能性覆盖。

ClearSpeed公司还在UVC基础上创建了自己的受限随机测试套件。相关覆盖在每次测试组运行之后都会进行分析,从而能清楚地理解覆盖漏洞出现在什幺地方,并指导新的测试应在什幺地方进行以到达未被覆盖的场景。这种方法还向ClearSpeed提供了无价的项目管理工具,因为它能帮助理解和报告验证状态。ClearSpeed公司能够在每个主要的规范领域正常地跟蹤覆盖、缺陷统计和测试故障。

工程背景

ClearSpeed公司的产品範围包括晶片、加速器卡、机架模组、软体和支持。ClearSpeed公司的晶片、加速器卡和机架模组都可以与工业标準的x86系统一起使用。ClearSpeed公司的晶片採用C语言进行编程,并且公司向用户提供可与所有标準软体开发工具协同工作的完整IDE.

与以前的CXS600晶片相比,主要变化如下:

⒈ 一个晶片上有两个处理器核心(“MTAP”)

⒉晶片上有一个标準的PCIe接口(相对私有PCIx接口而言)

⒊ MTAP有多项的改进

总体验证需求

图1给出了ClearSpeed产品的架构。为了确保这个複杂产品的质量,需要对以下性能进行验证:

⒈ 驱动程式代码与晶片的紧密集成

⒉ 众多软体库和应用程式的集成

⒊ 与各种主机(作业系统和晶片组)环境的兼容性

⒋ 高性能和低功率

从晶片本身看,主要验证挑战是最新引入的PCIe接口。为了应对这些验证挑战,ClearSpeed公司採用了一种适合待测複杂设计的先进验证策略。整个验证策略中有一些要点是可以明确的:

⒈ 这种验证策略是以仿真为基础,并採用了覆盖驱动的伪随机方法。

⒉ 使用了分层仿真策略,从模组级开始,并逐渐向外扩展。

⒊ 与软体的协同仿真非常重要,它有助于展示产品的正确性,并在晶片回厂时为硅片取得成功取得了良好开端。

⒋软体协同仿真也是分层执行的,从驱动程式开始,一直扩展到应用程式。

⒌ 模组和层次体系之间的验证再利用。

⒍ 使用验证IP。这样做有利于充分利用该领域专家的现有知识,并有利于加快测试平台的开发速度。

总的验证指导原则是在晶片开发初期从商业和技术角度获得签字确认标準。这些确认标準是客观性的,可以使用合适的準则进行测量。这样做具有很多优点,包括:

⒈ 能够使所有感兴趣方预先同意用于验证的对象。

⒉ 能够在项目执行中跟蹤向验证签字确认方向发展的进程。

⒊ 能够建立流片时的信心。

为了与上述原则保持一致,预先对CSX700验证确认标準进行了定义。所选的关键指标有:

⒈ 功能覆盖目标:

⑴ 优先权1覆盖目标达到100%

⑵ 所有其它覆盖目标至少达到95%,并检查所有未实现的覆盖目标。

⒉ 编写和支持的所有系统级测试。

⒊ 在所有可用PCIe伺服器中工作的原型PCIe。

⒋ 检查缺陷发现率以确保(与功能覆盖一起)我们正在接近所有最重要缺陷已经被发现的点。

⒌ 检查任何突出并已知未修复的问题,并评估它们的影响。

下面将在上文描述的总体验证策略框架下讨论PCIe验证策略。

模组级验证

PCIe模组级测试平台。ClearSpeed公司已经开发过图中所示的AVCI、PVCI和私有协定,因此PCIe接口提出了主要的验证挑战。由于我们使用的IP来自不同的管线PHY和端点核心供应商,因此这种挑战越发艰巨。

测试平台採用了许多UVC。除了PCIe UVC外,其它UVC都是ClearSpeed公司自己开发的。测试平台的其它部分使用公司自己的UVC有利于建立同质的eRM一致性系统(uRM和OVM)。

选用第三方ⅥP的原因是因为:PCIe协定的複杂性;验证任务的工作量以及缺少内部资源;ⅥP的成熟度;独立的ⅥP可以由与内部开发小组不相干的外部PCIe专家组开发。

系统级测试

系统级测试平台包括了晶片和软体驱动堆叠。实际的软体驱动程式基本原样投入使用,除了在堆叠底部做了一些修改,即将调用做进了仿真环境中,并由软体驱动PCIe UVC。更多细节请参考图4。在本例中,驱动程式完成与硬体对话要做的所有事情,并且每个事务都要传送给仿真器。这样运行起来虽然比较慢,但确实能让我们测试DMA引擎等。

驱动程式可以连线到PCIe层上面的仿真器。这样无需花费时间在完整仿真每个PCI事务上面就可以实现对更高层单元的仿真。这对仿真在处理器上运行的程式来说是非常有用的。

虽然通过使用UVC可以在测试规范允许的地方(例如在一些要写入的数据中,在定义範围内的地址中)使用受限随机激励,但在系统级主要套用定向测试方法。在系统级存在许多现成的定向测试,主要目标是用它们扩展测试这个晶片的变化(如前所列出的)。许多vPlanning会话被保持以获得测试规范,然后我们就能跟蹤这些测试的实现。一旦驱动程式堆叠经验证能与RTL一起工作,就可以运行较高层的软体。

运行这些应用程式能给功能验证和性能验证带来高度的信心。

在CSX700的开发过程中,ClearSpeed公司生产了一种基于现有硅片(CSX600)但用FPGA提供PCIe接口的产品,这样允许我们模拟PCIe接口并执行兼容性测试。也就是说,我们能将被模拟的PCIe接口连线到运行各种OS的众多伺服器上,从而在流片前确定兼容性问题。它还能让我们更彻底地测试带PCIe的软体驱动程式堆叠接口。

该方法可以识别主要位于PCIe堆叠物理层中的缺陷(FPGA中的PHY不同于我们晶片中的PHY),也让我们注意到我们连线的伺服器中PCIe实现的变化数量,并促使我们提升取得很高覆盖的重要性:我们对覆盖划分优先等级,并为最高优先权对象设定100%的目标。然而,该方法不能识别通过仿真&;覆盖也不能发现的PHY外的任何缺陷。这使我们相信,PCIe仿真中的高覆盖将有助于取得很高的首次流片成功率。

原型的其它优势还表现在软体开发方面。它能帮助PCIe软体驱动程式远早于CSX700硅片开发出来,加快基于CSX700的产品的上市时间。

验证环境

用于PCI Express的Incisive UVC能让用户专注于设计的任何部分或整个设计,并针对验证过程中每一阶段的特殊需要最佳化验证环境。Incisive UVC一般用于在模组、晶片和系统级对PCI Express器件进行功能验证。它也可以通过配置有选择地激活或关闭各个功能模组以及功能覆盖和检测机制来最佳化特殊任务的验证。这样可以提供到验证收敛的最可预测路径,并最大化在仿真器和工作站方面做出的投资回报。

自动激励产生

与使用上千次定向测试的其它解决方案不同,用于PCI Express的UVC採用自动激励发生器来减少用户需要做的工作量。利用包含所供序列库在内的自动化情景产生功能,用户可以覆盖主要协定功能以及难以到达的情景和边界案例。通过增加少量测试,剩余的边界案例就能被一一验证。这种方法有助于用户更快地发现更多缺陷,并让设计师有更多的时间进行DUT的私有功能测试。CMS可以实现整个过程的自动化。

CMS验证

CMS向用户提供了可执行的验证计画(vPlan)。vPlan与Enterprise Manager以及内置功能覆盖模型一起可以提供清晰地报告哪些被覆盖、还有哪些没被覆盖所需的标準。这给用户提供了验证过程的路线图、收敛标準以及可预测的验证过程,并向项目或管理方提供明晰的状态报告。这种方法被称为覆盖驱动的验证,可以帮助验证人员方便地识别覆盖漏洞,并将资源集中用于DUT的有问题部分。

Cadence的再利用方法可以快速建立功能验证环境,确保在从模组级验证向晶片级、系统级验证转移以及派生设计时能立即再利用基于UVC的环境。这种方法通过消除重複工作而节省了时间与资源。

优先权划分

通过使用能用来禁止掉与DUT无关的覆盖区/条目的“透视图(perspective)”,ClearSpeed公司能够只考虑与实现有关的覆盖点。ClearSpeed使用以下这个透视图:

“端点,AER = On,VC 1-7 = Off,完成器退出 = Off,配置请求重试状态 = Off,抑制 = Off"

CMS允许由主要的PCIe模组TPL、TXN、DLL、PHY、PMG、SYS和CONFIG报告覆盖,这有助于ClearSpeed公司根据技术风险划分验证工作的优先权。

我们认为物理层(PHY)存在较高的风险,因为物理层有两个不同的IP供应商,而且FPGA原型测试中没有覆盖PHY(因为FPGA使用不同的PHY);Power mgt是下一个最高优先权对象,因为在FPGA原型中没有覆盖到它(由于技术限制的原因);数据链路层是下一优先等级,因为它靠近PHY。

我们还要求更细颗粒的优先权划分:模组内的优先权划分。虽然一般来说可以使用透视图进行优先权划分,但这种方法不能满足所有需要和优先权划分的使用模型。它缺少更细的颗粒和一些对CMS专业用户(如ClearSpeed和IP开发人员)来说更重要的再利用因素。

测试套件

CMS提供的一致性测试可以使你一开始就有一个很好的基本覆盖,并因此而快速启动验证工作。ClearSpeed公司是比较早介入的,在整个项目中也在不断自我修正(附加的覆盖项目和一致性测试),因此一致性测试取得的覆盖在项目过程中会有变化。据Cadence公司估计,用户通过使用现成的CMS测试套件能够达到约70%的覆盖。

CMS测试也能经过配置进入PCIe协定的边界案例。然后,我们就可以写出许多自己的测试来驱动UVC达到想要的覆盖水平。

版本区别

PCI Express 2.0是PCI Express汇流排家族中的第二代版本。其中第一代的PCI Express 1.0标誌于2002年正式发布,它採用高速串列工作原理,接口传输速率达到2.5GHz,而PCI Express 2.0则在1.0版本基础上更进了一步,将接口速率提升到了5GHz,传输性能也翻了一番。新一代晶片组产品均可支持PCI Express 2.0汇流排技术,X1模式的扩展口频宽总和可达到1GB/s,X16图形接口更可以达到16GB/s的惊人频宽值。

硬体协定

PCIe的连线是建立在一个双向的序列的(1-bit)点对点连线基础之上,这称之为“传输通道”。与PCI 连线形成鲜明对比的是PCI是基于汇流排控制,所有设备共同分享的单向32位并行汇流排。PCIe是一个多层协定,由一个对话层,一个数据交换层和一个物理层构成。物理层又可进一步分为逻辑子层和电气子层。逻辑子层又可分为物理代码子层(PCS)和介质接入控制子层(MAC)。

物理层

各式不同的PCI Express插槽(由上而下:x4,x16,x1,与 x16),相较于传统的32-bit PCI插槽(最下方),取自于DFI的LanParty nF4 Ultra-D机板

于使用电力方面,每组流水线使用两个单向的低电压差分信号(LVDS)合计达到2.5兆波特。传送及接收不同数据会使用不同的传输通道,每一通道可运作四项资料。两个PCIe设备之间的连线成为“连结”,这形成了1组或更多的传输通道。各个设备最少支持1传输通道(x1)的连结。也可以有2,4,8,16,32个通道的连结。这可以更好的提供双向兼容性。(x2模式将用于内部接口而非插槽模式)PCIe卡能使用在至少与之传输通道相当的插槽上(例如x1接口的卡也能工作在x4或x16的插槽上)。一个支持较多传输通道的插槽可以建立较少的传输通道(例如8个通道的插槽能支持1个通道)。PCIe设备之间的连结将使用两设备中较少通道数的作为标準。一个支持较多通道的设备不能在支持较少通道的插槽上正常工作,例如x4接口的卡不能在x1的插槽上正常工作(插不入),但它能在x4的插槽上只建立1个传输通道(x1)。PCIe卡能在同一数据传输通道内传输包括中断在内的全部控制信息。这也方便了与PCI的兼容。多传输通道上的数据传输採取交叉存取,这意味着连续位元组交叉存取在不同的通道上。这一特性被称之为“数据条纹”,需要非常複杂的硬体支持连续数据的同步存取,也对连结的数据吞吐量要求极高。由于数据填充的需求,数据交叉存取不需要缩小数据包。与其它高速数传输协定一样,时钟信息必须嵌入信号中。在物理层上,PCIe採用常见的8B/10B代码方式来确保连续的1和0字元串长度符合标準,这样保证接收端不会误读。编码方案用10位编码比特代替8个未编码比特来传输数据,占用20%的总频宽。有些协定(如SONET)使用另外的编码结构如“不规则”在数据流中嵌入时钟信息。PCIe的特性也定义了一种“不规则化”的运算方法,但这种方法与SONET完全不同,它的方法主要用来避免数据传输过程中的数据重複而出现数据散射。第一代PCIe採用2.5兆位单信号传输率,PCI-SIG计画在未来版本中增强到5~10兆位。

数据连结层

数据连结层採用按序的交换层信息包(Transaction Layer Packets,TLPs),是由交换层生成,按32位循环冗余校验码(CRC,本文中用LCRC)进行数据保护,採用着名的协定(Ack and Nak signaling)的信息包。TLPs能通过LCRC校验和连续性校验的称为Ack(命令正确应答);没有通过校验的称为Nak(没有应答)。没有应答的TLPs或者等待逾时的TLPs会被重新传输。这些内容存储在数据连结层的快取内。这样可以确保TLPs的传输不受电子噪音干扰。

Ack和Nak信号由低层的信息包传送,这些包被称为数据连结层信息包(Data Link Layer Packet,DLLP)。DLLP也用来传送两个互连设备的交换层之间的流控制信息和实现电源管理功能。

交换层

PCI Express採用分离交换(数据提交和应答在时间上分离),可保证传输通道在目标端设备等待传送回应信息传送其它数据信息。它採用了可信性流控制。这一模式下,一个设备广播它可接收快取的初始可信信号量。连结另一方的设备会在传送数据时统计每一传送的TLP所占用的可信信号量,直至达到接收端初始可信信号最高值。接收端在处理完毕快取中的TLP后,它会回送传送端一个比初始值更大的可信信号量。可信信号统计是定製的标準计数器,这一算法的优势,相对于其他算法,如握手传输协定等,在于可信信号的回传反应时间不会影响系统性能,因为如果双方设备的快取足够大的话,是不会出现达到可信信号最高值的情况,这样传送数据不会停顿。第一代PCIe标称可支持每传输通道单向每秒250兆位元组的数据传输率。这一数字是根据物理信号率2500兆波特除以编码率(10位/每位元组)计算而得。这意味着一个16通道(x16)的PCIe卡理论上可以达到单向250*16=4000兆位元组/秒(3.7G位元组/每秒)。实际的传输率要根据数据有效载荷率,即依赖于数据的本身特性,这是由更高层(软体)应用程式和中间协定层决定。PCI Express与其它高速序列连线系统相似,它依赖于传输的鲁棒性(CRC校验和Ack算法)。长时间连续的单向数据传输(如高速存储设备)会造成>95%的PCIe通道数据占用率。这样的传输受益于增加的传输通道,但大多数应用程式如USB或乙太网络控制器会把传输内容拆成小的数据包,同时还会强制加上确认信号。这类数据传输由于增加了数据包的解析和强制中断,降低了传输通道的效率。这种效率的降低并非只出现在PCIe上。

技术套用

产品名称 | 详细参数 |

特科芯特科芯(TEKISM)PER970芯纪战舰系列 1TB PCI-E 固态硬碟 | 快取:128MB*5读写速度:最大读:2000MB/s 最大写:1970MB/s主控:Marvell +SF2200 系列主控颗粒:原厂东芝颗粒快闪记忆体类型:MLC原厂颗粒启动功率:写入:20W 空闲:12W尺寸:193.1*127.1*21.7(mm) 工作温度:0℃~-+60℃保存温度:-40℃~-+85℃ |

影驰9600GT中将版 | 晶片厂商:NⅥDIA 显示卡晶片:GeForce 9600GT 製造工艺:65纳米 显存类型:GDDR3 显存容量(MB):512 汇流排接口:PCI Express 2.0 16X 显存速度(ns):1.0ns 显存位宽:256bit 核心频率:650MHz 显存频率:1800MHz |

七彩虹逸彩9600GT-GD3 CF黄金版 512M N1 | 晶片厂商:NⅥDIA 显示卡晶片:GeForce 9600GT 製造工艺:55纳米 显存类型:GDDR3 显存容量(MB):512 显存速度(ns):1.0ns 汇流排接口:PCI Express 2.0 16X 显存位宽:256bit 核心频率:600MHz 显存频率:1800MHz |

七彩虹逸彩9800GT-GD3 冰封骑士3F 512M | 晶片厂商:NⅥDIA 显示卡晶片:GeForce 9800 GT 製造工艺:55纳米 显存类型:GDDR3 显存容量(MB):512 显存速度(ns):1.0ns 汇流排接口:PCI Express 2.0 16X 显存位宽:256bit 核心频率:600MHz 显存频率:1800MHz |

影驰9800GT+中将版 | 晶片厂商:NⅥDIA 显示卡晶片:GeForce 9800 GT 製造工艺:55纳米 显存类型:GDDR3 显存容量(MB):512 显存速度:0.8ns 汇流排接口:PCI Express 2.0 16X 显存位宽:256bit 核心频率:650MHz 显存频率:2200MHz |

影驰GTX260+上将 | 晶片厂商:NⅥDIA 显示卡晶片:GeForce GTX 260 製造工艺:55纳米 显存类型:GDDR3 显存容量(MB):896 显存速度:0.8ns 汇流排接口:PCI Express 2.0 16X 显存位宽:448bit 核心频率:625MHz 显存频率:2000MHz |

影驰9600GT节能加强版 | 晶片厂商:NⅥDIA 显示卡晶片:GeForce 9600GT 显存类型:GDDR3 显存容量(MB):512 汇流排接口:PCI Express 2.0 16X 显存速度:1.0ns 显存位宽:256bit 核心频率:600MHz 显存频率:1600MHz |

影驰9600GT加强版 | 晶片厂商:NⅥDIA 显示卡晶片:GeForce 9600GT 製造工艺:55纳米 显存类型:GDDR3 显存容量(MB):512 显存速度(ns):1.0ns 汇流排接口:PCI Express 2.0 16X 显存位宽:256bit 核心频率:650MHz 显存频率:1800MHz |

蓝宝石HD4850 512M 海外版 HDMI | 晶片厂商:ATI 显示卡晶片:Radeon HD 4850 製造工艺:55纳米 显存类型:GDDR3 显存容量(MB):512 显存速度(ns):1.0ns 汇流排接口:PCI Express 2.0 16X 显存位宽:256bit 核心频率:650MHz 显存频率:2000MHz |

nⅥDIA Quadro NVS 290 | 适用类型:工作站 製造工艺:80纳米 显存位宽:64bit 核心频率:300MHz 显示卡接口:PCI Express x16或PCI Express x1 DirectX版本:10 |

蓝宝石HD3850蓝曜天刃PRO 512MB | 晶片厂商:ATI 显示卡晶片:Radeon HD 3850 显存类型:DDRⅢ 显存容量(MB):512 显存位宽:256bit 汇流排接口:PCI Express 2.0 显存速度(ns):1.0ns |

影驰9600GTE上将版 | 晶片厂商:NⅥDIA 显示卡晶片:GeForce 9600GT 显存类型:DDRⅢ 显存容量(MB):512 显存位宽:256bit 汇流排接口:PCI Express 2.0 显存速度(ns):1.0ns |

4路採集卡

SVC404E是一款高性价比、高清晰度、质量稳定的PCI-E专业流媒体採集卡。该产品主要针对流媒体领域的要求,採用通用的 DirectShow 驱动架构,具有高效率的视频和声音採集能力。高性能的模拟视频前端滤波处理能力、高精度的音频採样能力,大大提升了视音频採集的清晰度。

注释

PCI Express是新一代能够提供大量频宽和丰富功能的新式图形架构。PCI Express可以大幅提高中央处理器(CPU)和图形处理器(GPU)之间的频宽。它可以给视频套用者更完美地享受影院级的图象效果,并获得无缝多媒体体验。

套用领域

基于网际网路流媒体线上直播、视频会议系统、VOD点播、远程监控、教学、 DVD製作,硬碟播出、广告截播、媒体资产管理。

技术特点

四路独立的视音频採集处理。

每路独立可以调成NTSC或PAL制。

四路视频输入和四路音频输入。

每路支持最大解晰度为NTSC:720x480;PAL:720X576。

支持大多数的视音频採集软体,如Media Encoder,Helix Real Producer等。

支持最大帧率30fps。

四路无压缩视音频数据DMA信道,使得四路视音频预览零CPU占用率。

高性能的模拟视频前端滤波处理能力,使原信号得到低码率高清晰的还原。

支持软体。

支持国内大多数视频会议软体,例如:AVCON视频会议系统、V2 Conference视频会议系统、网动视频会议系统。

支持Media Encoder,Helix Real Producer。

支持多种编码格式,包括:Wmv9,Rmvb,Rm,MPEG-4,DivX多格式视频编码,混合不同码率、解析度的视频同步流畅输出及播放。

实时预览,全文互式与处理硬体参数能力。

支持可程式时间触发(GPI,持续时调,自选键)。

从现存档案中进行最佳化转码(AⅥ/Quicktime/Quicktime类型档案)到多格式编码。

实际套用案例:

EP-H6200E MIL-STD-1553B/429/串口多协定通信PCI-E模组

EP-H6273E 1-2通道MIL-STD-1553B通讯PCI-E模组

EP-H6272E 16T/R ARINC429通讯PCI-E模组

EP-H6275E LVDS通讯接口PCI-E模组

EP-H6278E 双通道CAN汇流排通信PCI-E模组

EP-H6276E 16CH全异步RS-232/422串口通信PCI-E模组

EP-H6331E AD/DA/IO多功能PCI-E模组

EP-H6110E 1000MSPS 8Bit 1Ch数据採集PCI-E模组

EP-H6024AE 1MSPS12-Bit 8Ch数据採集PCI-E模组

EP-H6027AE 64MSps 14Bit 1CH ADC+DDC+DSP数据採集PCI-E模组

EP-H6033E 64SE/32DI数据採集PCI-E模组

EP-H6279E 1CH GPS接收PCI-E模组

EP-H6172E 16-Bit 8Ch 模拟输出PCI-E模组

EP-H6121CE 32通道隔离离散量输入/输出PCI-E汇流排模组

EP-H6121AE 64通道隔离开关量I/O PCI-E汇流排模组

EP-H6122CE 8CH标準RS-422电平计数器PCI-E汇流排模组

规范及改进

早在2007年上半年PCI-E 2.0版规范刚刚公布的时候,PCI Express技术标準组织PCI-SIG就準备用两年多的时间将其快速进化到第三代,但是谁也没想到PCI-E 3.0的酝酿过程会如此一波三折,直到今天才终于修成正果。

PCI-SIG主席兼总裁几乎泪流满面:“PCI-SIG始终致力于I/O创新,我们也很骄傲地向我们的成员发布PCI-E 3.0规范。PCI-E 3.0架构从细节上对前两代PCI-E规范进行了极大地改进,为我们的成员在各自领域继续创新提供了所必需的性能和功能。”

在对可製造性、成本、功耗、複杂性、兼容性等诸多方面进行综合、平衡之后,PCI-E 3.0规范将数据传输率提升到8GHz|8GT/s(最初也预想过10GHz),并保持了对PCI-E 2.x/1.x的向下兼容,继续支持2.5GHz、5GHz信号机制。基于此,PCI-E 3.0架构单信道(x1)单向频宽即可接近1GB/s,十六信道(x16)双向频宽更是可达32GB/s。

PCI-E 3.0同时还特别增加了128b/130b解码机制,可以确保几乎100%的传输效率,相比此前版本的8b/10b机制提升了25%,从而促成了传输频宽的翻番,延续了PCI-E规范的一贯传统。

新规范在信号和软体层的其他增强之处还有数据复用指示、原子操作、动态电源调整机制、延迟容许报告、宽鬆传输排序、基地址暂存器(BAR)大小调整、I/O页面错误等等,从而全方位提昇平台效率、软体模型弹性、架构伸缩性。

PCI-E 3.0规范完整文档现已向PCI-SIG组织成员公布其中详细描述了PCI-E架构、互联属性、结构管理、编程接口等等,但没有公开发表。另外,intel X79高端晶片组经已完整支持pci-e3.0规格,AMD最新架构旗舰显示卡AMD Radeon 7970,以及其他採用pci-e 3.0规格的显示卡将于2012年陆续发布。

AMD和HP将改进PCI Express 3.0规范

AMD和惠普公司的专家日前为PCI Express 3.0开发了两个新的扩展功能规范,藉由这两项新规范,除了可以降低相关微电路成本外还可以增加对多协定的支持,并且可以降低设备对中央处理器的访问频率。

开发人员希望他们的提案能够被发布的PCI-E 3.0规范所採纳。上述两个扩展功能并不互相依赖,它们主要套用于内置系统或高速系统的图形套用。第一个扩展功能被称为多路复用协定,它利用板卡上的一系列模组,实现PCI-E和其他7种不同的协定之间的动态切换。利用该功能,我们可以构建这样一个解决方案:通过PCI-E接口,处理器和显示卡通过QPI(Quick Path Interconnect)或者HT(Hyper Transport)连线。

第二个扩展功能被称为轻信息,它允许协处理器及外围设备在存储系统的支持下,通过PCI-E接口互相通信,而不必再经过中央处理器。例如,乙太网交换机可以不通过中央处理器而独立的编码和解码数据。

另外,这两项扩展功能适用于工作频率为2.5GHz、5GHz和8GHz版本的PCI-E规范。

PCI-E 3.0规范向下兼容PCI-E 2.0和PCI-E 1.0,最高传输速度可达32GB/s,有望在2010年出现相关产品。

PCI Express 2.0和PCI Express16的区别

PCI-E 2.0相对于1.0来说,的确是名副其实的双倍规格:

频宽翻倍:将单通道PCI-E X1的频宽提高到了500MB/s,也就是双向1GB/s;

通道翻倍:显示卡接口标準升级到PCI-E X32,频宽可达32GB/s;

插槽翻倍:晶片组/主机板默认应该拥有两条PCI-E X32插槽;

功率翻倍:目前PCI-E插槽所能提供的电力最高为75W,2.0版本可能会提高至200W以上,还不确定中。

PCI-Express是当前主流的汇流排和接口标準,它原来的名称为“3GIO”,是由Intel提出的,很明显Intel的意思是它代表着下一代I/O 接口标準。交由PCI-SIG(PCI特殊兴趣组织)认证发布后才改名为“PCI-Express”。这个新标準将全面取代现行的PCI和AGP,最终实现汇流排标準的统一。1990年引进PCI汇流排接口时,由于其具有处理器独立性、缓冲隔绝以及汇流排控制和随插即用等机制及特性,不久之后便一举统一了包含ISA、VESA、VL BUS、EISA以及MCA等汇流排规格,成为个人计算机中的汇流排插槽主流。

不过其运作频率的进步不若中央处理器那般突飞猛进,因此在面对新一代的扩充卡及周边时,已经有力不从心的感觉,而共享式的设计,单一高速周边(如Gb乙太网络或IEEE 1394b)可能就会将PCI的所有频宽吃光。虽然针对特定用途也有高频率或具备独立频宽的版本(如PCI-X和AGP)出现,但是成本的高昂以及使用上的限制,这些特殊规格PCI并没有成为通用标準。

于2007年1月通过的PCI Express 2.0标準,除了在维持与PCI Express 1.1版兼容性的前提下,对单一通道宽度倍增以外(由原先2.5Gbps提升至5Gbps),并且在原有的特性之下加入了几项先进的功能,以期更为符合未来的需求。

I/O Vitualization-可套用于包括设备共享、地址转换服务(ATS)以及单/多处理器系统的单独规格。可提供给多部虚拟机器共享多种包含网卡等I/O设备,有助于系统管理者在开发以及管理上的方便性。

更强的安全保护机制-可允许软体来看至互连的封包路由,以防止被不良意图人士进行欺骗以及窃取封包数据,或者是对于数据进行假路由,在未来PCI Express 2.0规范中,这个特性将会被包含在晶片组、交换晶片以及多功能组件之中。

可自动调整的连结速度-当连结频宽或速率下降时,控制软体将会自动侦测并且对硬体进行通报,而自动对连结速度进行调整,动态配置PCI Express汇流排的信道。

更高的供电规格-未来高阶显示卡将会更为耗电,比如说NⅥDIA即将在11月发表的G80(代号)绘图卡,其耗电量可能高达300W左右,1.1版的PCI Express规范只能提供70W左右,完全不敷及未来高阶显示卡之用,因此在2.0版规范中,将供电能力大幅提升至300W左右。

PCI Express缆线连线规范-这是属于新的套用,就如同SATA连线规范中有一个eSATA的外部在线上标準,缆线化的PCI Express可提供更为灵活的使用性,比如说计算机的网路、储存或显示组件就不必连线至计算机主机板上,只要透过缆线连结,显示周边与储存周边都可以拥有独立的电源以及配置空间。甚至也可以进行伺服器之间的互连,达到丛集的目的。

除了以上所提到的以外,更为高速的PCI Express也可以提供整合型图形晶片对主存储器更高的读取速度,不过依照以往的经验,在这方面的改进对于整合型图形晶片的效能增长可能并不会很大,影响效能的主要因素还是在于绘图晶片本身的设计。

不过高速序列架构不仅只于PCI Express一家而已,类似架构的标準还有HyperTransport、Infiniband、RapidIO以及StarFabric等,这些竞争对手也都有各自庞大势力在支撑。除了背后势力以外,在技术上也不见得会输给PCI Express,比如说Infiniband、StarFabric可藉软体追蹤拓朴结构变化,以实现热插拔功能,而HyperTransport及RapidIO则是可藉由减少封包大小来加快反应速度,相较起来,PCI Express则是显得较为中庸,延伸套用较少。

截至2006年底,PCI Express已经成为个人计算机主机板的标準,由于其完全透明的软体层设计让软硬体开发者可以在利用最少资源的情况下得到最好的效能表现,不仅成为高阶3D加速卡的指定连线方式,对消费者来说,也成为了效能表现的代名词。至于PCI Express在笔记型计算机上的延伸标準ExpressCard,虽然面世已有一段时间,但是在支持周边仍不够丰富的情况之下,仅少数笔记型计算机厂商具有较全面的支持。

1990年引进PCI汇流排接口时,由于其具有处理器独立性、缓冲隔绝以及汇流排控制和随插即用等机制及特性,不久之后便一举统一了包含ISA、VESA、VL BUS、EISA以及MCA等汇流排规格,成为个人计算机中的汇流排插槽主流。

不过其运作频率的进步不若中央处理器那般突飞猛进,因此在面对新一代的扩充卡及周边时,已经有力不从心的感觉,而共享式的设计,单一高速周边(如Gb乙太网络或IEEE 1394b)可能就会将PCI的所有频宽吃光。虽然针对特定用途也有高频率或具备独立频宽的版本(如PCI-X和AGP)出现,但是成本的高昂以及使用上的限制,这些特殊规格PCI并没有成为通用标準。

为了因应下一代周边的I/O频宽需求,以及对于整体架构上的统一化设计,Intel结合各大IT厂商,制订出PCI-Express规格。PCI-Express架构中,包含了五个堆叠层,其中与过去PCI架构在软体层(载入储存架构以及平面地址空间)方面的兼容性,确保了现存应用程式与驱动程式不需要做出任何变革即可正常运作。而由于PCI-Express在设定组态上,也同样使用了过去套用在PCI上的随插即用标準机制。软体层以封包为基础的设计,并且藉由分割执行的通讯协定,产生可由执行曾传送至I/O装置的读取以及写入需求。而连结层则是为这些封包加入编号以及错误修正码,以求达到可靠的数据传输结果。至于在传输实体层方面,则是实作了包含一传输对以及一接收对的双重单通道,每个方向皆具备有2.5Gbps的初始速度,而且可以藉由增加讯号对,以行成多路径来线性扩展。以一个信道2.5Gbps的速度为传输基础,在实体曾提供了x1、x2、x4、x8、x16以及x32等代表信道数量以及路径宽度来表示其实际传输速度。

pci Express把伺服器带入新纪元

pci Express的传输速度已经达到20甚至100Gbps,pci Express具备即插即用与可扩展性,这些都是数据中心经理们梦寐以求的,当然也是需要衡量性价比的。

需要看一下底层的技术:pci Express。pci Express诞生于2004年,pci Express是一些自协定的合集,具有物理层、数据链路层与传输层标準定义。pci Express听起来是OSI网路模型的一部分,而且就像网路一样,你可以改变物理层。

pci Express只出现在电脑内部,但2011年之后所谓的Thunderbolt接口将pci Express接口扩展到了机箱外。

Thunderbolt接口非常快,传输速度在20Gbps,但其实际上是pci Express的不同物理转接方式。事实上你还可以使用具有普通pci Express插槽的扩展Thunderbolt外壳。Thunderbolt被认为是光学组件,基于Intel硅光子学设计,而且Thunderbolt对非IT消费者来说是非常具有性价比的选择

pci Express对系统管理的影响十分显着。想想,如果你的存储阵列是个即插即用的设备?不管你不信,但pci Express确实发生了。插上伺服器,Windows Update会搜寻驱动程式,pci Express接着将其分配到一个存储组,大功告成。你还希望繁琐、容易出错的存储管理方式吗?这同样还适用于网路。当谁需要IP时,你可以通过远程直接访问记忆体,将IP直接写入。pci Express自动化是一块创可贴;这种分类管理方法是对IT複杂性问题发起的一次挑战。

pci Express是Intel即将商品化的领域,pci Express在多方面拥有巨大的好处:标準、成本、灵活性、运营成本,甚至资本支出。pci Express可以整合所有IT,pci Express不再利用乙太网和IP连结所有2U机箱,pci Express是将其全部接到分散式背板上。