PCIe意义 是PCI的更高发展 PCIe比以前的标準有许多改进,包括更高的最大系统汇流排吞吐量,更低的I/O引脚数量和更小的物理尺寸,更好的汇流排设备性能缩放,更详细的错误检测和报告机制(高级错误报告,AER)和本机热插拔功能。 PCIe标準的更新版本为I/O虚拟化提供了硬体支持。

PCI Express电接口也用于各种其他标準,最值得注意的是作为笔记本电脑扩展卡接口的ExpressCard以及作为计算机存储接口的SATA Express。

PCI Express 2.0规范的主要在数据传输速度上做出了重大升级,即从以前的2.5GT/s汇流排频率翻倍至5GT/s,这也就是说以前PCI Express 2.0 x16接口能够翻番达到惊人的8GB/s汇流排频宽(1GB/s=8Gbps)。

目前最新的版本为PCI-E 3.0,是生产中可用于主流个人电脑的扩展卡的最新标準。也有还未退市的PCI-E(即1.0版)。而在2009年的第二季度发布的AMD RD890晶片组将率先支持PCI-E 3.0版本。2.0比1.0频宽提高一倍,而3.0比2.0版频宽又提升一倍,为5GHz x 4。

2.0升级部分 1、重点是PCI Express汇流排频率提升:每条串列线路的数据传输率从2.5Gbps翻番至5Gbps,频宽也随之翻倍。

2、可更好地支持未来高端显示卡,即使功耗达到225W或者300W也只需PCI Express单独供电即可。

3、新增“输入输出虚拟化”(IOV)技术,可以让多台虚拟机共享网卡等PCI设备。

4、PCI-E线缆子规范可让PCI设备通过标準化铜缆线接入计算机,而且每条线路的速度都能达到2.5Gbps,适用于为高端伺服器加入多块网卡作为输入输出扩展模组等场合。

5、最后是代号“Geneseo”的长期规划。该技术与Intel、IBM等业界巨头合作开发,可让图形处理单元、加密处理单元等协处理器更好地与中央处理器紧密相连。

6、对动态链路速度和链路宽度管理、以及活动状态电源管理(ASPM)进行相关改进。

角色定位 EMC公司最近更新的快取策略巩固了固态PCI Express在伺服器中的地位,并将和其他IT厂商一起为提升企业数据存储的效率扮演重要的角色。

但是PCI Express flash是否从根本上影响了整个行业以及是否对典型的数据中心具有吸引力仍然值得讨论。固态存储技术具有两面性,IT企业对新挑战还是抱有谨慎的态度。但是没人会否认PCIe不论是在快取还是在主存里提升的优越性能。

PCIe的主要优势在于其减少延迟的能力。PCIe设备和PCIe汇流排直接相连,使快取和数据更接近CPU。他们消除了传统存储协定的开销,并且EMC认为在合适的条件下能实现远远优于从08年开始销售的串列SCSI和SATA的固态硬碟SSD的性能。

PCIE规格 传输通道数

脚Pin总数

主接口区Pin数

总 长 度

主接口区 长度

1

36

14

25 mm

7.65 mm

4

64

42

39 mm

21.65 mm

8

98

76

56 mm

38.65 mm

16

164

142

89 mm

71.65 mm

规格

汇流排宽度

工作时脉

传输速率

PCI-E x1

8 位

2.5 GHz

512 MiB/s

PCI-E x2

8 位

2.5 GHz

1.0 GiB/s

PCI-E x4

8 位

2.5 GHz

2.0 GiB/s

PCI-E x8

8 位

2.5 GHz

4.0 GiB/s

PCI-E x16

8 位

2.5 GHz

8.0 GiB/s

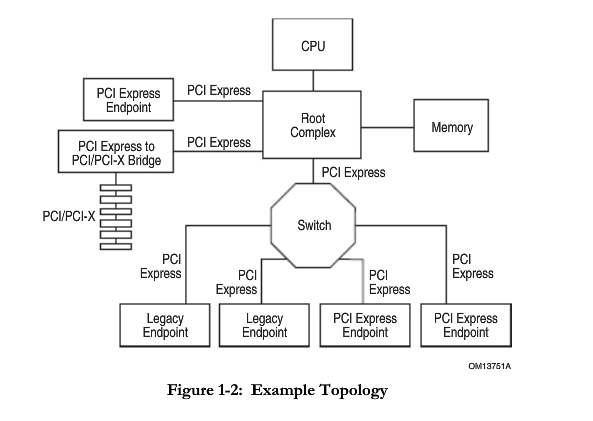

结构 在概念上,PCI Express汇流排是较旧的PCI/ PCI-X汇流排的高速串列替换。PCI Express汇流排与旧PCI之间的主要区别之一是汇流排拓扑。 PCI使用共享并行汇流排架构,其中PCI主机和所有设备共享一组通用的地址,数据和控制线。 相比之下,PCI Express基于点到点拓扑,单独的串列链路将每个设备连线到根系统(主机)。 由于其共享汇流排拓扑,可以对单个方向上的PCI汇流排进行仲裁(在多个主机的情况下),并且一次限制为一个主机。 此外,旧的PCI时钟方案将汇流排时钟限制在汇流排上最慢的外设(不管汇流排事务中涉及的设备如何)。 相比之下,PCI Express汇流排链路支持任何两个端点之间的全双工通信,同时跨多个端点的并发访问没有固有的限制。

在汇流排协定方面,PCI Express通信封装在数据包中。打包和解包数据和状态讯息流量的工作由PCI Express连线埠的事务层处理,电信号和汇流排协定的根本差异需要使用不同的机械外形尺寸和扩展连线器(因此,需要新的主机板和新的适配器板); PCI插槽和PCI Express插槽不可互换。在软体级别,PCI Express保留与PCI的向后兼容性; 传统的PCI系统软体可以检测和配置较新的PCI Express设备,而无需显式支持PCI Express标準,但是新的PCI Express功能无法访问。两个设备之间的PCI Express链路可以由1个到32个通道组成。 在多通道链路中,分组数据在通道上条带化,并且峰值数据吞吐量与整个链路宽度成比例。通道计数在设备初始化期间自动协商,并且可以被任一端点限制。例如,单通道PCI Express(×1)卡可以插入多通道插槽(×4,×8等),初始化周期自动协商最高相互支持的通道数。该连结可以动态地自动配置自己,以便使用较少的通道,在存在不良或不可靠的通道的情况下提供故障容限。PCI Express标準定义了多个宽度的插槽和连线器:×1,×4,×8,×12,×16和×32。这允许PCI Express汇流排服务于不需要高吞吐量的成本敏感型套用,以及诸如3D图形,网路(万兆乙太网或多连线埠千兆位乙太网)和企业级存储(SAS或光纤通道)等关键性能的套用。

作为参考,使用四路(×4)的PCI-X(133MHz 64位)设备和PCI Express 1.0设备具有大致相同的峰值单向传输速率为1064MB / s。 在多个设备同时传输数据的情况下,或者与PCI Express外设的通信是双向的情况下,PCI Express汇流排具有比PCI-X汇流排更好的性能。

互连 PCI Express设备通过称为互连或链路的逻辑连线进行通信。链路是两个PCI Express连线埠之间的点对点通信通道,允许它们传送和接收普通PCI请求(配置,I / O或存储器读/写)和中断(INTx,MSI或MSI-X) 。 在物理层面上,一条链路由一条或多条通道组成。低速外设(例如802.11 Wi-Fi卡)使用单通道(×1)链路,而图形适配器通常使用更宽更快的16通道链路。

通道 通道由两个差分信号对组成,一对用于接收数据,另一对用于传送。 因此,每个通道由四条线或信号迹线组成。在概念上,每条通道用作全双工位元组流,在链路端点之间的两个方向同时传输8位“位元组”格式的数据包。物理PCI Express链路可能包含1个到32个通道,更精确地包括1,2,4,8,12,16或32个通道。通道计数用“×”前缀( 例如“×8”表示八通道卡或插槽),×16是常用的最大尺寸。

串列汇流排 由于后者的固有限制,包括半双工操作,超量信号计数以及由于定时偏移引起的固有的较低频宽,因此,传统的并行汇流排选择了绑定串列汇流排架构。定时偏移来自在不同长度的导线,潜在不同的印刷电路板(PCB)层和可能不同的信号速度下行进的并行接口内的分离的电信号。儘管作为单个字同时传输,并行接口上的信号具有不同的行进持续时间,并在不同时间到达其目的地。当接口时钟周期短于信号到达之间的最大时间差时,就不可能恢复传输的字。由于并行汇流排上的定时偏移量可能达到几纳秒,因此所产生的频宽限制在几百兆赫的範围内。

串列接口不会出现定时偏移,因为每个通道中每个方向只有一个差分信号,并且由于时钟信息嵌入在串列信号本身中,所以没有外部时钟信号。因此,串列信号的典型频宽限制在几千兆赫範围内。 PCI Express是串列互连替代并行汇流排的一般趋势的一个例子;其他示例包括Serial ATA(SATA),USB,Serial Attached SCSI(SAS),FireWire(IEEE 1394)和RapidIO。在数字视频中,常用的例子有DVI,HDMI和DisplayPort。

多通道串列设计增加了灵活性,其能够为较慢的设备分配较少的通道。

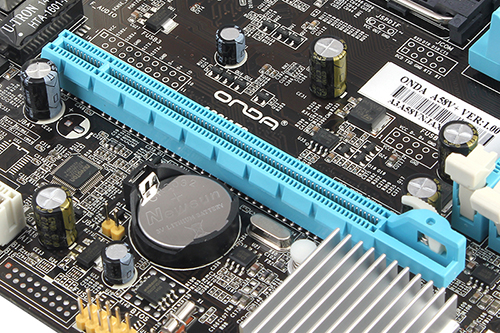

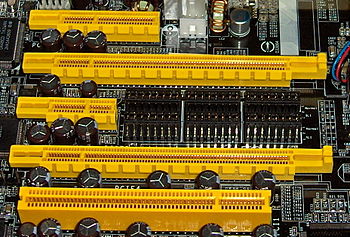

形式参数 PCIe标準 PCI Express卡适合其物理尺寸或更大的插槽(使用×16作为最大的),但可能不适合更小的PCI Express插槽;例如,×16卡可能不适合×4或×8插槽。一些插槽使用开放式插座来允许物理上更长的卡,并协商最佳的电子和逻辑连线。

350px-PCIExpress 实际连线到插槽的通道数量也可能少于物理槽大小所支持的数量。一个例子是一个×16插槽可以运行×1、×2、×4、×8、×16的卡,当运行×4卡时只提供4条通道。其规格可以读为“×16(×4模式)”,而“×size @×速度”符号(“×16 @×4”)也是常见的。优点是这样的插槽可以容纳更大範围的PCI Express卡,而不需要主机板硬体来支持全传输速率。

卡本身设计和製造各种尺寸。例如,以PCI Express卡形式出现的固态驱动器(SSD)通常使用HHHL(半高,半长)和FHHL(全高,半长)来描述卡的物理尺寸。(右图中上面四个为PCIe插槽,最下面一个为PCI插槽)

引脚排列 下表列出了PCI Express卡上边缘连线器每侧的导线。 印刷电路板(PCB)的焊接侧为A侧,元件侧为B侧。PRSNT1#和PRSNT2#引脚必须稍短于其他引脚,以确保热插拔卡完全插入。WAKE#引脚使用全电压唤醒计算机,但必须从备用电源拉高以指示卡是可以唤醒。

PCIe 连线器引脚(× 1 、× 4 、× 8 和× 16 变体)

引脚

B 侧

A 侧

描述

引脚

B 侧

A 侧

描述

1

+12V

PRSNT1#

必须连线到最远的PRSNT2 #

50

HSOp(8)

保留

通道8传输数据,+和-

2

+12V

+12V

主电源引脚

51

HSOn(8)

地面

3

+12V

+12V

52

地面

HSIp(8)

通道8接收数据,+和-

4

地面

地面

53

地面

HSIn(8)

5

SMCLK

TCK

SMBus和JTAG连线埠引脚

54

HSOp(9)

地面

通道9传输数据,+和-

6

SMDAT

TDI

55

HSOn(9)

地面

7

地面

TDO

56

地面

HSIp(9)

通道9接收数据,+和-

8

+3.3V

TMS

57

地面

HSIn(9)

9

TRST#

+3.3V

58

HSOp(10)

地面

通道10传输数据,+和-

10

+3.3V aux

+3.3V

备用电源

59

HSOn(10)

地面

11

激活#

复位#

连结激活;复位

60

地面

HSIp(10)

通道10接收数据,+和-

关键的缺口

61

地面

HSIn(10)

12

CLKREQ#

地面

请求运行时钟

62

HSOp(11)

地面

通道11传输数据,+和-

13

地面

REFCLK+

参考时钟差分对

63

HSOn(11)

地面

14

HSOp(0)

REFCLK−

通道0传输数据,+和-

64

地面

HSIp(11)

通道11接收数据,+和-

15

HSOn(0)

地面

65

地面

HSIn(11)

16

地面

HSIp(0)

通道0接收数据,+和-

66

HSOp(12)

地面

通道12传输数据,+和-

17

PRSNT2#

HSIn(0)

67

HSOn(12)

地面

18

地面

地面

68

地面

HSIp(12)

通道12接收数据,+和-

PCI Express×1卡在引脚18处结束

69

地面

HSIn(12)

19

HSOp(1)

保留

通道1传输数据,+和-

70

HSOp(13)

地面

通道13传输数据,+和-

20

HSOn(1)

地面

71

HSOn(13)

地面

21

地面

HSIp(1)

通道1接收数据,+和-

72

地面

HSIp(13)

通道13接收数据,+和-

22

地面

HSIn(1)

73

地面

HSIn(13)

23

HSOp(2)

地面

通道2传输数据,+和-

74

HSOp(14)

地面

通道14传输数据,+和-

24

HSOn(2)

地面

75

HSOn(14)

地面

25

地面

HSIp(2)

通道2接收数据,+和-

76

地面

HSIp(14)

通道14接收数据,+和-

26

地面

HSIn(2)

77

地面

HSIn(14)

27

HSOp(3)

地面

通道3传输数据,+和-

78

HSOp(15)

地面

通道15传输数据,+和-

28

HSOn(3)

地面

79

HSOn(15)

地面

29

地面

HSIp(3)

通道3接收数据,+和-

80

地面

HSIp(15)

通道15接收数据,+和-

30

保留

HSIn(3)

81

PRSNT2#

HSIn(15)

31

PRSNT2#

地面

82

保留

地面

32

地面

保留

PCI Express×4卡在引脚32处结束

33

HSOp(4)

保留

通道4传输数据,+和-

34

HSOn(4)

地面

35

地面

HSIp(4)

通道4接收数据,+和-

36

地面

HSIn(4)

37

HSOp(5)

地面

通道5传输数据,+和-

38

HSOn(5)

地面

39

地面

HSIp(5)

通道5接收数据,+和-

40

地面

HSIn(5)

41

HSOp(6)

地面

通道6传输数据,+和-

42

HSOn(6)

地面

43

地面

HSIp(6)

通道6接收数据,+和-

Legend

44

地面

HSIn(6)

接地引脚

零伏

45

HSOp(7)

地面

通道7传输数据,+和-

电源引脚

为PCIe卡供电

46

HSOn(7)

地面

卡到主机引脚

从卡到主机板的信号

47

地面

HSIp(7)

通道7接收数据,+和-

主机到卡引脚

从主机板到卡的信号

48

PRSNT2#

HSIn(7)

开漏

可能拉低或由多张卡感应

49

地面

地面

感应针

绑在一张卡上

PCI Express×8卡在引脚49处结束

保留

目前不使用,请勿连结

电源 所有PCI Express卡在+ 3.3V(9.9W)可能消耗高达3A。它们可能消耗的+12V和总功率取决于卡的类型:

·×1卡在+ 12V(6W)和10W组合时限制为0.5A。

·×4和更宽的卡在+ 12V(25W)和25W组合时限制为2.1A。

·在初始化和软体配置为“大功率设备”后,一个全尺寸×1卡可能会达到25 W限制。

·在初始化和软体配置为“大功率设备”后,一个全尺寸×16显示卡可以在+ 12V(66 W)和75 W组合后可能会达到5.5A限制。

可选连线器增加75 W(6引脚)或150 W(8引脚)+12 V电源,然后可以达到总共300 W(2×75 W + 1×150 W)。一些卡使用两个8针连线器,但这还没有标準化,因此这种卡不能携带官方的PCI Express标誌。该配置允许总共375 W(1×75 W + 2×150 W),并且可能会通过PCI-SIG与PCI Express 4.0标準进行标準化。 8针PCI Express连线器可能与EPS12V连线器混淆,EPS12V连线器主要用于为SMP和多核系统供电。

PCI Express迷你卡 基于PCI Express的PCI Express迷你卡(也称为Mini PCI Express,Mini PCIe,Mini PCI-E,mPCIe和PEM)是Mini PCI外形尺寸的替代品。 它是由PCI-SIG开发的。 主机设备支持PCI Express和USB 2.0连线,每个卡都可以使用任一标準。 大多数笔记本电脑2005年之后构建使用PCI Express进行扩展卡; 然而,截至2015年,许多供应商正在为此目的使用较新的M.2外形尺寸。

由于尺寸不同,PCI Express迷你卡与标準全尺寸PCI Express插槽不兼容; 然而,存在允许它们在全尺寸插槽中使用的被动适配器。

1、物理尺寸

PCI Express迷你卡的尺寸为全迷你卡的30×50.95毫米(宽度×长度)。 有一个52针边缘连线器,由0.8 mm间距的两个交错行组成。 每行有八个触点,一个间隙相当于四个触点,然后另外18个触点。 板的厚度为1.0毫米,不包括部件。 还规定了“半迷你卡”(有时简称为HMC),其大约一半的物理长度为26.8毫米。

2、电接口

PCI Express迷你卡边缘连线器提供多种连线和汇流排:

·PCI Express×1(带SMBus)

·USB 2.0

·用于诊断计算机机箱上无线网路LED(即Wi-Fi)状态的电线

·用于GSM和WCDMA套用的SIM卡(规格为UIM信号)。

·另一个PCIe通道的未来扩展

·1.5 V和3.3 V电源

3、Mini-SATA(mSATA)变体

儘管共享Mini PCI Express外形,但是mSATA插槽不一定与Mini PCI Express兼容。因此,仅某些笔记本与mSATA驱动器兼容。大多数兼容系统都是基于英特尔的Sandy Bridge处理器架构,使用了Huron River平台。 2011年3月至4月发布的联想ThinkPad T,W和X系列笔记本电脑在WWAN卡槽中支持mSATA SSD卡。 ThinkPad Edge E220s / E420s以及Lenovo IdeaPad Y460 / Y560也支持mSATA。

一些笔记本电脑(特别是华硕Eee PC,苹果MacBook Air以及戴尔mini9和mini10)使用PCI Express迷你卡作为固态硬碟。该变体使用预留和几个非保留引脚来实现SATA和IDE接口直通,只保留USB,地面线,有时候还有核心PCIe×1汇流排保持不变。这使得“miniPCIe”快闪记忆体和固态驱动器出售上网本大部分与真正的PCI Express Mini实现不兼容。

此外,典型的华硕miniPCIe SSD长71毫米,导致戴尔51毫米的型号经常被错误地称为半长。 2009年宣布推出一款真正的51 mm Mini PCIe SSD,具有两个堆叠的PCB层,可以提供更高的存储容量。被宣布的设计中保留了PCIe接口,使其与标準的mini PCIe插槽兼容。目前还没有工业产品开发。

英特尔拥有众多台式机主机板,其PCIe×1迷你卡插槽通常不支持mSATA SSD。在英特尔支持网站上提供了PCIe x1 Mini-Card插槽(通常与SATA连线埠复用)本机支持mSATA的台式机主机板列表。

4、迷你PCIe v2

新版本的Mini PCI Express,M.2替代了mSATA标準。 通过M.2连线器提供的计算机汇流排接口是PCI Express 3.0(最多四个通道),Serial ATA 3.0和USB 3.0(后两者的单个逻辑连线埠)。 这取决于主机支持和设备类型的所需级别,由M.2主机或设备的製造商决定要支持哪些接口。

5、PCI Express外部布线

PCI Express外部电缆PCI Express外部布线(也称为外部PCI Express,电缆PCI Express或ePCIe)规格由PCI-SIG于2007年2月发布。

标準电缆和连线器已定义为×1,×4,×8和×16链路宽度,每个通道的传输速率为250 MB / s。 PCI-SIG也期望规范将演进到500 MB / s,如PCI Express 2.0。 最大电缆长度保持不变。 使用电缆PCI Express的一个例子是一个金属外壳,其中包含许多PCI插槽和PCI-to-ePCIe适配器电路。 如果没有ePCIe规范,此设备将无法实现。

衍生形式 其他几种类型的扩展卡来自PCIe,这些包括:

·高低卡

·ExpressCard:PC卡的后续版本(带×1个PCIe和USB 2.0;可热插拔)

·PCI Express ExpressModule:为伺服器和工作站定义的热插拔模组化形式

·XQD卡:CompactFlash协会的基于PCI Express的快闪记忆体卡标準

·XMC:类似于CMC / PMC外形(VITA 42.3)

·AdvancedTCA:对更大套用的CompactPCI的补充;支持基于串列的背板拓扑

·AMC:对AdvancedTCA规范的补充;支持ATCA板上的处理器和I / O模组(×1,×2,×4或×8 PCIe)。

·FeaturePak:适用于嵌入式和小型套用的小型扩展卡格式(43×65 mm),可在高密度连线器以及USB,I2C和多达100个I / O点上实现两个1 PCIe连线

·通用IO:Super Micro Computer Inc的一款变体,专门用于低调机架式机箱。它的连线器支架相反,因此它不能装在普通的PCI Express插座中,但它是引脚兼容的,如果拆下支架,可以插入。

·Thunderbolt:Intel的一个变体,它结合了DisplayPort和PCIe协定,与Mini DisplayPort兼容。 Thunderbolt 3.0还结合了USB 3.1,并使用USB Type-C外形尺寸,而不是Mini DisplayPort。

·串列数字视频输出:一些9xx系列英特尔晶片组允许将集成视频的另一个输出添加到PCIe插槽(主要是专用和16通道)。

·M.2(以前称为NGFF)

·M-PCIe通过M-PHY物理层将PCIe 3.0带到移动设备(如平板电脑和智慧型手机)

·U.2(以前称为SFF-8639)

历史版本 在早期开发中,PCIe最初被称为HSI(用于高速互连),并在最终确定其PCI-SIG名称PCI Express之前,将其名称更改为3GIO(第三代I / O)。 名为阿拉帕霍工作组(AWG)的技术工作组制定了该标準。 对于初稿,特设工作组只包括英特尔工程师; 随后特设工作组扩大到包括行业伙伴。

PCI Express是一项不断发展和完善的技术。

截至2013年,PCI Express版本4已经起草,预计在2017年将达到最终规格。在2016年PCI SIG的年度开发者大会上和英特尔开发者论坛上,Synopsys展示了一款在PCIe 4.0上运行的系统,而Mellanox提供了一个合适的网卡。

PCI Express 版本

行代码

传输速率

吞吐量

×1

×4

×8

×16

1.0

8b/10b

2.5GT/s

250MB/s

1GB/s

2GB/s

4GB/s

2.0

8b/10b

5GT/s

500MB/s

2GB/s

4GB/s

8GB/s

3.0

128b/130b

8GT/s

984.6MB/s

3.938GB/s

7.877GB/s

15.754GB/s

4.0

128b/130b

16GT/s

1.969GB/s

7.877GB/s

15.754GB/s

31.508GB/s

5.0

128b/130b

32 or 25GT/s

3.9 or 3.08GB/s

15.8 or 12.3GB/s

31.5 or 24.6GB/s

63.0 or 49.2GB/s

PCIe 1.0a 2003年,PCI-SIG推出了PCIe 1.0a,每通道数据速率为250 MB / s,传输速率为每秒2.5 gigatransfer(GT / s)。 传输速率表示为每秒传输量,而不是每秒位数,因为传输量包括不提供额外吞吐量的开销位; PCIe 1.x使用8b / 10b编码方案,导致占用了20% (= 2/10)的原始信道频宽。

PCIe 1.1 2005年,PCI-SIG推出了PCIe 1.1。 此更新的规范包括澄清和几项改进,但与PCI Express 1.0a完全兼容。 数据速率没有变化。

PCIe 2.0 PCI-SIG于2007年1月15日宣布推出PCI Express Base 2.0规范。PCIe 2.0标準将PCIe 1.0至5 GT / s的传输速率提高了一倍,每通道吞吐量从250 MB / s上升到500 MB / s。因此,32通道PCIe连线器(×32)可支持高达16 GB / s的总吞吐量。

PCIe 2.0主机板插槽与PCIe v1.x卡完全向后兼容。 PCIe 2.0卡也通常使用PCI Express 1.1的可用频宽向下兼容PCIe 1.x主机板。总体来说,为v2.0设计的显示卡或主机板将与另一个v1.1或v1.0a配合使用。

PCI-SIG还表示,PCIe 2.0具有对点对点数据传输协定及其软体架构的改进。

英特尔首款支持PCIe 2.0的晶片组是X38,截至2007年10月21日,各种厂商(Abit,Asus,Gigabyte)开始出货。AMD开始使用其AMD 700晶片组系列支持PCIe 2.0,nVidia从MCP72开始。Intel的所有晶片组,包括Intel P35晶片组,都支持PCIe 1.1或1.0a。

像1.x一样,PCIe 2.0使用8b / 10b编码方案,因此每通道提供5 GT / s原始数据速率的有效4 Gbit / s最大传输速率。

PCIe 2.1 PCI Express 2.1(其规范日期为2009年3月4日)支持计画在PCI Express 3.0中全面实施的大部分管理,支持和故障排除系统。 但是,速度与PCI Express 2.0相同。 不幸的是,插槽功率的增加打破了PCI Express 2.1卡和1.0 / 1.0a的一些较旧的主机板之间的向后兼容性,但是大多数具有PCI Express 1.1连线器的主机板都由厂商通过实用程式提供BIOS更新,以支持向后兼容性 的PCIe 2.1。

PCIe 3.0 PCI Express 3.0基本规范版本3.0在多个延迟之后于2010年11月提供。 2007年8月,PCI-SIG宣布PCI Express 3.0将以每秒8吉比特的速度(GT / s)进行比特率,并且将与现有的PCI Express实现向后兼容。当时还宣布,PCI Express 3.0的最终规范将延迟到2010年第二季度。PCI Express 3.0规范的新功能包括增强信令和数据完整性的一些最佳化,包括发射机和接收机均衡,PLL改进,时钟数据恢复和当前支持的拓扑的通道增强。

PCI-SIG的分析发现,在PCI-SIG互连频宽扩展的可行性方面进行了为期6个月的技术分析,发现每秒8个千兆传输速率可以在主流硅工艺技术中製造,并且可以部署在现有的低成本材料和基础设施上,同时保持对PCI Express协定栈的完全兼容性(可忽略不计的影响)。

PCI Express 3.0将编码方案从之前的8b / 10b编码升级到128b / 130b,将频宽开销从PCI Express 2.0的20%降低到大约1.54%(= 2/130)。这通过称为“加扰”的技术来实现,该技术将已知的二进制多项式套用于反馈拓扑中的数据流。因为加扰多项式是已知的,所以可以通过使用反多项式的反馈拓扑运行数据来恢複数据。 PCI Express 3.0的8 GT / s比特率有效地提供每通道985 MB / s,实际上相对于PCI Express 2.0的通道频宽翻倍

2010年11月18日,PCI特别兴趣小组正式向其成员发布了完成的PCI Express 3.0规范,以便根据新版本的PCI Express构建设备。

PCIe 3.1 2013年9月,PCI Express 3.1规格已经宣布在2013年底或2014年初发布,在三个方面整合了PCI Express 3.0规范的各种改进:电源管理,性能和功能它于2014年11月发布。

PCIe 4.0 2011年11月29日,PCI-SIG宣布PCI Express 4.0提供16Gb / s比特率,使PCI Express 3.0提供的频宽增加一倍,同时保持软体支持和二手机械接口的向后兼容性。 PCI Express 4.0规格也将带来OCuLink-2,这是Thunderbolt连线器的替代品。 OCuLink版本2将具有高达16 GT / s(总共8GB / s×4通道),而Thunderbolt 3连线器的最大频宽为5GB / s。 另外,还要研究主动和空闲功率最佳化。 最终规格预计将于2017年发布。

在2016年8月,Synopsys在英特尔开发者论坛上展示了运行PCIe 4.0的测试机。 他们的智慧财产权已经授权给几家计画在2016年底提供其晶片和产品的公司。

PCI-E SD 7.0 2018年6月,SD协会已经基本完成了全新一代SD 7.0标準规范的制定工作,计画在2018年6月26-28日上海举办的MWC大会上正式公布。

扩展和未来方向 一些供应商提供PCIe光纤产品,但这些通常仅在特定情况下才能使用,其中透明PCIe桥接优于使用更主流的标準(如InfiniBand或乙太网),可能需要额外的软体支持它当前的实现集中于距离而不是原始频宽,并且通常不实现全×16链路。

Thunderbolt由英特尔和苹果公司共同开发,作为将DisplayPort连线埠组合在一起的通用高速接口,最初旨在成为全光纤接口,但由于创建消费者友好的光纤互连大多数早期实现是混合铜纤维系统。一个显着的例外,Sony VAIO Z VPC-Z2使用带有光学组件的非标準USB连线埠连线到外置PCIe显示适配器。苹果一直是2011年Thunderbolt採用的主要动力,儘管其他几家供应商已经宣布推出具有Thunderbolt的新产品和系统。

移动PCIe规范(缩写为M-PCIe)允许PCI Express架构在MIPI Alliance的M-PHY物理层技术上运行。基于已经广泛採用的M-PHY及其低功耗设计,移动PCIe允许PCI Express在平板电脑和智慧型手机中使用。

OCuLink(代表“光铜链路”)是“电缆版PCI Express”的扩展,作为Thunderbolt接口版本3的竞争对手。将于2015年秋季发布的OCuLink版本1.0支持通过铜缆布线的PCIe 3.0 x4通道(8 GT / s,3.9 GB / s)光纤版可能会在将来出现。

硬体协定摘要 PCIe链路是围绕称为通道的串列(1位)点对点连线的专用单向耦合的。 这与早期的PCI连线形成鲜明对比,PCI连线是基于汇流排的系统,其中所有设备共享相同的双向32位或64位并行汇流排。

PCI Express是一种分层协定,由事务层,数据链路层和物理层组成。 数据链路层被细分为包括媒体访问控制(MAC)子层。 物理层被细分为逻辑和电子子层。 物理逻辑子层包含物理编码子层(PCS)。 这些术语借鉴了IEEE 802网路协定模型。

物理层 PCIe物理层(PHY,PCIEPHY,PCI Express PHY或PCIe PHY)规范分为两个子层,对应于电气和逻辑规范。逻辑子层有时被进一步划分为MAC子层和PCS,儘管该划分不是PCIe规范的正式部分。英特尔公布的PCI Express(PIPE)PHY接口(58)定义了MAC / PCS功能分区以及这两个子层之间的接口。 PIPE规范还标识了物理介质连线(PMA)层,其中包括串列器/解串器(SerDes)和其他模拟电路;然而,由于SerDes实现在ASIC供应商之间差异很大,PIPE没有指定PCS和PMA之间的接口。

在电平上,每个通道由两个以2.5,5,8或16 Gbit / s为单位的单向LVDS对组成,具体取决于协商的能力。传送和接收是单独的差分对,每个通道总共有四条数据线。

任何两个PCIe设备之间的连线称为链路,并且由一个或多个通道的集合构建。所有设备必须最低限度地支持单通道(×1)链路。设备可以可选地支持由2,4,8,12,16或32个通道组成的更宽的链路。这样可以通过两种方式实现非常好的兼容性:

PCIe卡在任何至少与其一样大的插槽中物理适配(并且正常工作)(例如,x尺寸的卡将在任何大小的插槽中工作);

只要提供较大物理槽所需的地面连线,则物理尺寸较大(例如×16)的槽可以更少的通道连线(例如,×1,×4,×8或×12)尺寸。

在这两种情况下,PCIe协商最高相互支持的通道数。验证了许多显示卡,主机板和BIOS版本,以支持同一连线上的×1,×4,×8和×16连线。

儘管这两者将是信号兼容的,但通常不可能将一个物理上更大的PCIe卡(例如,×16尺寸的卡)放置在较小的插槽中 - 儘管如果PCIe插槽被更改或者使用了提升板,大多数主机板会允许这个。 PCIe连线器的宽度为8.8 mm,高度为11.25 mm,长度可变。连线器的固定部分长度为11.65mm,包含两行11(总共22个),另一部分的长度根据通道数量而变化。引脚以1mm间隔隔开,进入连线器的卡的厚度为1.8mm。

数据传输

PCIe通过与数据相同的连结传送所有控制讯息,包括中断。串列协定永远不会被阻止,所以延迟仍然与具有专用中断线的常规PCI相当。

在多通道链路上传送的数据被交织,这意味着每个连续的位元组被连续通过。 PCIe规范将这种交织作为数据条带化。在需要大量硬体複杂性来同步(或去偏移)输入条带数据的同时,条带化可以显着减少链路上第n个位元组的延迟。虽然通道没有紧密同步,但对于2.5 / 5/8 GT / s,通道偏差为20/8/6 ns,因此硬体缓冲区可以重新对齐条带数据。由于填充要求,条带化可能不一定会降低链路上的小数据包的等待时间。

与其他高数据速率串列传输协定一样,时钟嵌入在信号中。在物理层面上,PCI Express 2.0使用8b / 10b编码方案来确保连续相同数字(零或1)的字元串的长度有限。该编码用于防止接收机丢失位边缘的位置。在这种编码方案中,每个八(未编码)有效载荷数据位被替换为传送数据的10(编码)比特,导致电频宽中的20%开销。为了提高可用频宽,PCI Express 3.0版代替使用128b / 130b编码加扰。 128b / 130b编码依赖于加扰来限制数据流中相同数字串的运行长度,并确保接收机保持同步到发射机。它还通过防止传送的数据流中的重複数据模式来降低电磁干扰(EMI)。

数据链路层 数据链路层为PCIe Express链路执行三个重要服务:

对由事务层生成的事务层数据包(TLP)进行排序,

通过确认协定(ACK和NAK信令)确保在两个端点之间可靠地传递TLP,这些确认协定明确要求重播未确认/不良TLP,

初始化和管理流量控制信用

在传送侧,数据链路层为每个输出TLP生成递增序列号。它作为每个传输的TLP的唯一标识标籤,并被插入到出站TLP的头部。 32位循环冗余校验码(在本上下文中称为链路CRC或LCRC)也附加到每个输出TLP的末尾。

在接收端,接收的TLP的LCRC和序列号都在链路层中被验证。如果LCRC检查失败(指示数据错误)或序列号超出範围(从上一次有效接收到的TLP不连续),则坏TLP以及在坏TLP之后接收的任何TLP,被认为是无效和被丢弃。接收方向无效TLP的序列号传送一个否定的确认讯息(NAK),请求重新传送该序列号的所有TLP。如果接收的TLP通过LCRC检查并具有正确的序列号,则被视为有效。链路接收器增加序列号(跟蹤最后接收的良好TLP),并将有效的TLP转发到接收者的事务层。 ACK讯息被传送到远程发射机,指示TLP被成功地接收(并且扩展了所有具有过去序列号的TLP)。

如果发射机接收到NAK讯息,或者在逾时时间段到期之前没有接收到确认(NAK或ACK),则发射机必须重发所有缺少肯定确认(ACK)的TLP。除了设备或传输介质的持续故障之外,链路层提供与事务层的可靠连线,因为传输协定确保在不可靠介质上传送TLP。

除了传送和接收由事务层生成的TLP之外,数据链路层还生成并消耗DLLP,数据链路层数据包。 ACK和NAK信号通过DLLP进行通信,流控信用信息,一些电源管理讯息和流控信用信息(代表事务层)也是如此。

实际上,链路上的未确认TLP的数量受到两个因素的限制:发射机的重播缓冲区的大小(必须存储所有传送的TLP的副本,直到远程接收机确认它们),以及流量控制接收机发给发射机的信用。 PCI Express要求所有接收者发出最少数量的信用,以保证一个链路允许传送PCIConfig TLP和讯息TLP。

事务层 PCI Express实现拆分事务(具有请求和回响时间间隔的事务),允许连结携带其他流量,而目标设备收集回响的数据。

PCI Express使用基于信用的流量控制。在该方案中,设备在其事务层中为每个接收到的缓冲器通告初始信用量。连结相对端的设备在向该设备传送交易时,会计算每个TLP从其帐户中消耗的信用数量。传送设备只能在这样做时才传输TLP,使其消费的信用计数不超过其信用限额。当接收设备从其缓冲区完成TLP的处理时,它向传送设备发出信用回报信号,从而将信用额度增加了恢复的数量。信用计数器是模组化计数器,消费信用与信用限额的比较需要模数运算。这种方案的优点(与其他方法,如等待状态或基于握手的传输协定相比)是信用回报的延迟不会影响性能,前提是不会遇到信用额度。如果每个设备设计有足够的缓冲区大小,则通常满足这一假设。

经常引用PCIe 1.x,以支持每个方向每个通道250 MB / s的数据速率。这个数字是从物理信令速率(2.5千兆位)除以编码开销(每个位元组10位)的计算。这意味着十六行(×16)PCIe卡理论上能够达到16×250 MB / s =每个方向4 GB / s。虽然这在数据位元组方面是正确的,但更有意义的计算是基于可用的数据有效载荷速率,这取决于流量的简档,这是高级(软体)应用程式和中间协定级别的函式。

像其他高数据速率串列互连繫统一样,由于附加的传输鲁棒性(CRC和确认),PCIe具有协定和处理开销。长时间连续的单向传输(例如高性能存储控制器中的那些)可以接近PCIe的原始(通道)数据速率的95%。这些转移也可以从增加通道数量(×2,×4等)中获得最大收益。但是在更典型的套用(如USB或乙太网控制器)中,流量简档的特徵是具有频繁强制确认的短数据包。由于分组解析和强制中断(在设备的主机接口或PC的CPU)中的开销,这种流量会降低链路的效率。作为连线到相同印刷电路板的设备的协定,它不需要与用于长距离通信的协定的传输错误相同的容限,因此这种效率的损失对于PCIe不是特别的。

套用 PCI Express在消费者,伺服器和工业套用中运行,作为主机板级互连(连线主机板外围设备),无源背板互连以及作为附加板的扩展卡接口。

在几乎所有现代(截至2012年)PC(从消费者笔记本电脑和台式机到企业数据伺服器)中,PCIe汇流排作为主要的主机板级互连,将主机系统处理器与集成外设(表面贴装IC)连线起来,和附加外设(扩展卡)。在大多数这些系统中,PCIe汇流排与一个或多个传统PCI汇流排共存,以便与大量传统PCI外设的向后兼容。

截至2013年,PCI Express已将AGP替换为新系统上显示卡的默认界面。 AMD(ATI)和Nvidia自2010年以来发布的几乎所有型号的显示卡都使用PCI Express。 Nvidia使用PCIe的高频宽数据传输作为其可扩展链路接口(SLI)技术,它允许同一晶片组和型号的多个显示卡串联运行,从而提高性能。 AMD还开发了基于PCIe的多GPU系统,称为CrossFire。 AMD和Nvidia发布了支持多达四个PCIe×16插槽的主机板晶片组,允许三GPU和四GPU卡配置。

外部GPU 理论上,通过将笔记本电脑与任何PCIe桌面显示卡(封装在自己的外部外壳中,具有强大的电源和散热)连线,外部PCIe可以为笔记本电脑提供桌面的图形功能;可能使用ExpressCard接口或Thunderbolt接口。 ExpressCard接口提供5 Gbit / s(0.5 GB / s吞吐量)的比特率,而Thunderbolt接口提供高达40 Gbit / s(5 GB / s吞吐量)的比特率。

2010年推出的外部卡集线器可以通过PCI ExpressCard插槽连线到笔记本电脑或台式机。这些集线器可以接受全尺寸显示卡。示例包括MSI GUS, Village Instrument的ViDock,华硕XG站,Bplus PE4

Asus Nvidia GeForce GTX 650 Ti H V3.2适配器以及更多即兴DIY设备。然而,这样的解决方案受到笔记本电脑上可用的PCIe插槽的大小(通常只有x1)和版本的限制。

2008年,AMD宣布推出ATI XGP技术,该技术基于与PCIe×8信号传输兼容的专有布线系统。富士通Amilo和Acer Ferrari One笔记本电脑提供此连线器。富士通此后推出了针对XGP的AMILO GraphicBooster外壳。2010年左右,宏碁推出了XGP的Dynavivid图形码头英特尔霹雳接口给了新的和更快速的产品与外部与PCIe卡连线的机会。 Magma发布了ExpressBox 3T,可容纳三个PCIe卡(两个在×8,一个在×4)。MSI还发布了专门用于显示卡的PCIe底盘Thunderbolt GUS II。其他产品,如Sonnet的Echo Express和mLogi的mLink是Thunderbolt PCIe机箱,尺寸较小然而,所有这些产品都需要具有Thunderbolt连线埠(即Thunderbolt设备)的计算机,例如,苹果Macbook Pro在2013年秋季发布。

对于专业市场,Nvidia开发了可用于高级图形套用的Quadro Plex外部PCIe系列GPU。这些视频卡需要一个PCI Express×8或×16插槽,用于通过支持8个PCIe通道的VHDCI连线到Plex的主机侧卡。

存储设备 PCI Express协定可用作快闪记忆体设备的数据接口,如存储卡和固态硬碟(SSD)。

An_Intel_82574L_Gigabit_Ethernet_NIC XQD卡是使用由CompactFlash协会开发的PCI Express的存储卡格式,传输速率高达500 MB / s

许多高性能企业级SSD被设计为具有直接放置在电路板上的快闪记忆体晶片的PCI Express RAID控制器卡,利用专有接口和定製驱动程式与作业系统进行通信;与串列ATA或SAS驱动器相比,这允许高得多的传输速率(超过1 GB / s)和IOPS(每秒超过一百万个I / O操作)例如,2011年,OCZ和Marvell共同开发了一款用于PCI Express 3.0×16插槽的本地PCI Express固态驱动器控制器,最大容量为12 TB,性能达到7.2 GB / s,连续传输和高达252万随机转移中的IOPS。

SATA Express是连线SSD的接口,通过为连线的存储设备提供多个PCI Express通道作为纯PCI Express连线。M.2是内部安装的计算机扩展卡和相关连线器的规范,也使用多个PCI Express通道。

PCI Express存储设备可实现AHCI逻辑接口以实现向后兼容,还可实现NVM Express逻辑接口,通过利用此类设备提供的内部并行性提供更快的I / O操作。企业级SSD也可以通过PCI Express实现SCSI。

群集互连 某些数据中心套用(如大型计算机集群)由于铜线缆固有的距离限制,需要使用光纤互连。 通常,诸如乙太网或光纤通道的面向网路的标準对于这些套用来说足够,但是在某些情况下,由可路由协定引入的开销是不期望的,并且需要诸如InfiniBand,RapidIO或NUMAlink之类的较低级别的互连。 本地汇流排标準(如PCIe和HyperTransport)原则上可以用于此目的,但截至2015年,解决方案只能从海豚供应商(如海豚ICS)获得。

SATA_6_Gbit-s_controller,_in_form_of_a_PCI_Express_card PCI-E 3.0 常见的显示卡都是PCI-E 2.0标準的,制定于2007年,速率5GT/s,x16通道频宽可达8GB/s。按照原先的路线图,PCI-E 3.0标準将在2010年进入市场,不过实际上却是2010年才完成PCI-E 3.0标準的最终方案,而直到一年后HD 7970发布才真正有显示卡支持PCI-E 3.0。

PCI-E 3.0:频宽更高、延迟更低

与PCI-E 2.0相比,PCI-E 3.0的目标是频宽继续翻倍达到10GB/s,要实现这个目标就要提高速度,PCI-E 3.0的信号频率从2.0的5GT/s提高到8GT/s,编码方案也从原来的8b/10b变为更高效的128b/130b,其他规格基本不变,每周期依然传输2位数据,支持多通道并行传输。

除了频宽翻倍带来的数据吞吐量大幅提高之外,PCI-E 3.0的信号速度更快,相应地数据传输的延迟也会更低。此外,针对软体模型、功耗管理等方面也有具体最佳化。简而言之,PCI-E 3.0就跟高速路一样,车辆跑得更快,发车间隔更低,座位更舒适。

PCI-E 3.0 要求 ·支持多个细分市场和新兴套用:

统一桌面,移动,工作站,伺服器,通信平台和嵌入式设备的I / O架构;

·提供低成本,大批量解决方案的能力:

成本在系统级以下PCI成本结构或以下

·支持多平台互联使用:

晶片到晶片,板对板连线器或电缆

·新的机械外形:

移动式,类似PCI的外形尺寸和模组化,车架尺寸

·PCI兼容软体模型:

能够枚举和配置PCI Express硬体,无需修改即可使用PCI系统配置软体实现,;

无需修改即可启动现有作业系统

无需修改即可支持现有I / O设备驱动程式,

能够配置/ 通过PCI实现新的PCI Express功能

·性能:

·低开销,低延迟通信,最大限度地提高套用有效载荷频宽和链路效率;

·每个引脚的高频宽,最大限度地减少每个设备的引脚数和连线器接口;

·通过聚合通道和信号频率可扩展的性能

高级功能:

了解不同的数据类型和排序规则,电源管理和预算,

识别给定功能的电源管理功能

·将功能转换为特定电源状态

·接收功能当前电源状态通知

·产生从主电源关闭状态唤醒的请求,

·将设备上电顺序的能力设定为允许在功率预算中实现平稳的平台策略

支持差异化服务的能力,即不同的服务质量

能够为服务质量的数据流量提供专用的链路资源,以提高面向线路阻塞的结构效率和有效的套用级性能

在每个组件中配置服务质量仲裁策略

能够标记每个数据包的端到端服务质量

创建端到端等时(基于时间,注入速率控制)解决方案

·热插拔和热插拔支持

支持现有PCI热插拔和热插拔解决方案

支持本地热插拔和热插拔解决方案(无需框线信号)

支持所有形式因素的统一软体模型

·数据完整性:

·支持所有类型的事务和数据链路数据包的链路级数据完整性

·支持高可用性解决方案的端到端数据完整性

·故障处理:

·能够支持高级错误报告和处理,以改进故障隔离和恢复解决方案

·工艺技术独立性:

·在发射机和接收机上支持不同直流共模电压

·易于测试:

·通过简单连线测试设备测试符合性

PCI Express 链路 一个链路表示两个组

件之间的双单工通信通道。基本的PCI Express链路由两个低电压,差分驱动信号对组成:传送对和接收对,如图所示

基本连结: PCI Express链路由双向单向差分链路组成,实现为传送对和接收对。使用编码方案嵌入数据时钟以实现非常高的数据速率

信令速率: 一旦初始化,每个链路只能在支持的信令级别之一运行。对于第一代PCI Express技术,只有一个信令速率被定义,提供有效的每秒每通道每个方向2.5吉比特的原始频宽。第二代提供有效的每秒每通道每个方向8.0吉比特的原始频宽。随着未来的技术进步,数据速率预计将增加。

通道 :链路必须支持至少一个通道,每个通道表示一组差分信号对(一对用于传输,一对用于接收)。为了缩放频宽,链路可以聚合由xN表示的多个通道,其中N可以是任何 的支持链路宽度。以2.5GT / s数据速率运行的x8链路表示每个方向的原始频宽为20千兆位的聚合频宽

初始化 :在硬体启动期间,每个PCI Express链路都是在链路两端的两个代理商的通道宽度和操作频率协商后设定的。没有固件或作业系统软体

对称性: 每个链路必须支持对称数,如果在每个方向上的通道,即x16链路指示在每个方向上存在16个差异信号对

PCI Express Fabric拓扑 结构是由连线一组组件的点对点链路组成,一个示例性结构拓扑如图1-2所示。这个图说明了一个层次结构的单个结构实例,由一个根複合体组成,多个端点(I / O设备),交换机和PCI Express标準的 PCI / PCI-X桥接器,均通过PCI Express链路互连。

PCI-E 4.0 PCI Express 3.0是企业计算的记忆,微处理器,网路和存储之间的通信的主要标準,但它正面临新的竞争,因为其即将到来的重大更新是一些最重要的观察者所压倒的。

控制规范的PCI-SIG官员在五年前就谈到了他们的第四代计画,并表示版本4.0将于2015年到期。现在,新的延迟,加上大数据,网际网路的最新趋势物联网和移动计算领域正在推动数个顶尖IT厂商採用新的数据瓶颈方法。

据了解,PCIe 4.0将以每秒16千兆位传输的速度移动数据,这是当前版本的两倍。 PCI-SIG主管的工程师,IBM的Al Yanes解释说,这可以通过使用更短时间传送大量数据的突发方法来实现当前电压水平的一半或四分之一。

Yanes去年宣布,PCIe 4.0将在今年年初推出。现在,由于测试问题,“我认为在循环推出之前的第三季度会更多,”他说。他补充说,直到最近还没有太多的需求。

PCIe 4.0,具有16GT / s的数据速率和新的连线器将在2017年完成。

PCI Express汇流排已经发展十多年了。到目前为止,技术的初始数据速率已翻了三倍,但下一步是花费更长的时间。 PCI SIG声称,第四代PCI Express规范将于2017年完成,并将在这十年中实现。新技术将使用新的连线器,并将是PCI Express的最后一个铜版本。

PCI SIG [特殊兴趣小组]自2011年年底以来一直在开发PCI Express 4.0。新车的目标数据速率为每通道16GT / s [每秒千兆转发],组织一直设定这个目标,即使许多没有相信使用宽泛的铜线互连汇流排是可行的。该标準尚未定稿,因为参与者必须同意许多参数,包括互连属性,结构管理以及设计和构建符合PCI Express 4.0规范的系统和外设所需的编程接口。

例如,到目前为止,PCI SIG尚未就没有重新定时器的PCIe 4.0轨迹的最大长度达成一致。许多套用,如伺服器和通信设备,需要更长的互连。

PCI SIG总裁Al Yanes在接受EE Times採访时表示:“我们正在获得16GT / s,几年前没有人想到可能。” “基地距离仍在验证中,但通常为7英寸左右。 15英寸左右的两个连线器的更长的通道将具有重新定时器,但第3代已经使用了重新定时器 - 现在我们需要将它们用于较短的通道。

竞争协定 基于高频宽串列架构的其他通信标準包括InfiniBand,RapidIO,HyperTransport,Intel QuickPath Interconnect和移动行业处理器接口(MIPI)。差异基于灵活性和可扩展性与延迟和开销之间的权衡。例如,将複杂的报头信息添加到传输的分组允许複杂路由(PCI Express能够通过可选的端到端TLP前缀功能)。额外的开销降低了接口的有效频宽,并使汇流排发现和初始化软体複杂化。此外,使系统可热插拔要求软体跟蹤网路拓扑变化。 InfiniBand是一种这样的技术。

另一个例子是使数据包更短以减少延迟(如果汇流排必须作为存储器接口运行,则需要这样做)。较小的数据包意味着数据包头消耗的数据包的百分比较高,从而降低了有效频宽。为此目的设计的汇流排协定的例子是RapidIO和HyperTransport。

PCI Express位于中间的某个地方,以设计为目标,作为系统互连(本地汇流排),而不是设备互连或路由网路协定。此外,其软体透明度的设计目标限制了协定并稍微提高了其延迟。

PCIe 4.0实现的延迟导致了Gen-Z联盟,CCIX的努力和一个开放的Coherent Accelerator处理器接口(CAPI),全部在2016年底之前被公布。

350px-PCIExpress

350px-PCIExpress Asus Nvidia GeForce GTX 650 Ti

Asus Nvidia GeForce GTX 650 Ti An_Intel_82574L_Gigabit_Ethernet_NIC

An_Intel_82574L_Gigabit_Ethernet_NIC SATA_6_Gbit-s_controller,_in_form_of_a_PCI_Express_card

SATA_6_Gbit-s_controller,_in_form_of_a_PCI_Express_card